aishakhan

Newbie level 5

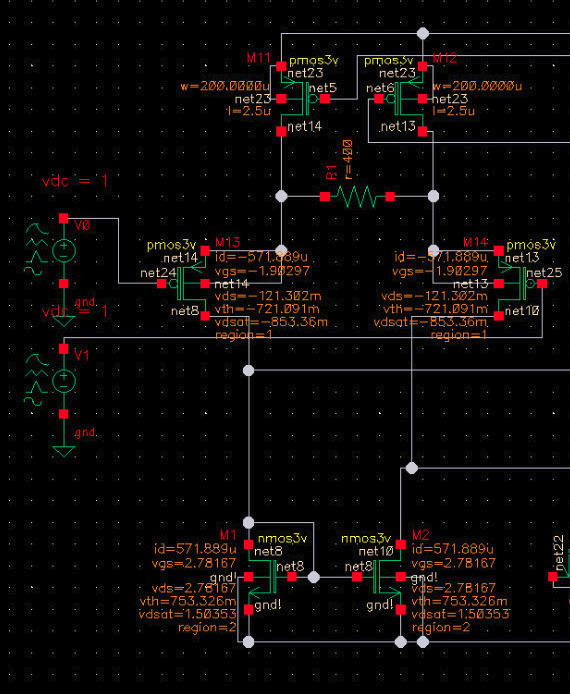

Hi, I'm new here and also I'm new to Analog IC Design, actually I'm implementing an IA design which was in 350nm technology node, and I'm implementing it in 180nm. I'm having this issue that the MOSFETS need to operate in sat region, but they're operating in triode region. Could anyone tell me what to do so that my mosfets all work in the saturation region? Here's an attached image of the design: M11, M12, M13, and M14 all are in triode region, and I need it to be operating in saturation region. Any help would be really appreciated. Regards.