TunerPhish

Junior Member level 3

Hi

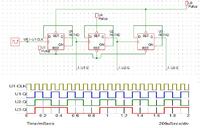

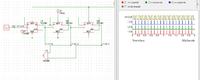

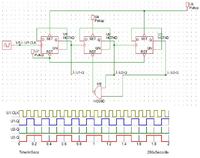

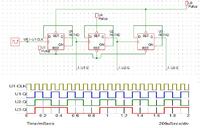

I am trying to design a Mod 6 3-Bit D-type asynchronous down counter using Pspice and I am having difficulty with the Nand gate in order to make the count go from 5-0. In its present state it is counting from 7-0 and I know with the addition of adding a NAND gate I can reduce the count to the desire 5-0 but I have no idea how to connect the gate up in Pspice. I have tried various positions but cannot get the desired output.

Can anybody help me out as to where to connect the gate? I have added an image of the construction so far.

I am trying to design a Mod 6 3-Bit D-type asynchronous down counter using Pspice and I am having difficulty with the Nand gate in order to make the count go from 5-0. In its present state it is counting from 7-0 and I know with the addition of adding a NAND gate I can reduce the count to the desire 5-0 but I have no idea how to connect the gate up in Pspice. I have tried various positions but cannot get the desired output.

Can anybody help me out as to where to connect the gate? I have added an image of the construction so far.