esdeath_123

Junior Member level 3

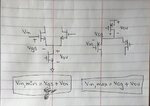

So, I've encountered two stage miller with PMOS differential pair as input while others have NMOS differential pair input. Are there any advantages/disadvantages of using one over the other? When is it preferable to use a PMOS differential pair as input and when is it preferable to use NMOS differential pair as input?

If you can recommend or know references or materials that discuss this deeply, it would be greatly appreciated. Thanks!

If you can recommend or know references or materials that discuss this deeply, it would be greatly appreciated. Thanks!