020170

Full Member level 4

optical proximity correction

Hello

I have a question on metal width variation in CMOS Process, especially nano meter process

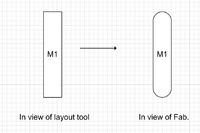

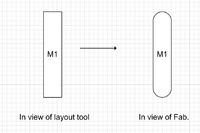

Metal line that I draw looks like square Line in layout tool. but in real metal line was not square line. it looks like rather round square line owing to etch processing. (see following Fig.)

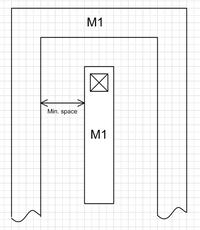

In some case, Metal Line go round via or other metal line with minimum DRC rule. (see following Fig. metal line turns around other metal and via )

In this case, All metal width was reduced rather than the real size of metal width.

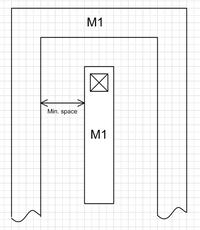

However, Only One Metal line was laid on some place, and there was no other metal near here, Metal width was increased rather than decreased by process variation. ( see following fig. no any other metal, this metal width is increased )

I witness this phenomenon today. but I don't explain why this phenomenon occur in very different way.

There is anyone who explain me in detail?

Thanks.

Hello

I have a question on metal width variation in CMOS Process, especially nano meter process

Metal line that I draw looks like square Line in layout tool. but in real metal line was not square line. it looks like rather round square line owing to etch processing. (see following Fig.)

In some case, Metal Line go round via or other metal line with minimum DRC rule. (see following Fig. metal line turns around other metal and via )

In this case, All metal width was reduced rather than the real size of metal width.

However, Only One Metal line was laid on some place, and there was no other metal near here, Metal width was increased rather than decreased by process variation. ( see following fig. no any other metal, this metal width is increased )

I witness this phenomenon today. but I don't explain why this phenomenon occur in very different way.

There is anyone who explain me in detail?

Thanks.