LakshmiJL

Junior Member level 2

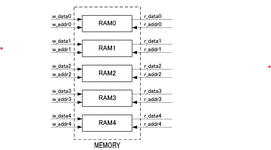

I need to divide a memory into multiple memory banks(more than 2) and write data to each of the memory bank simultaneously. In this case how is the write and read operation managed. Should I have same number of read and write ports as that of the memory bank?Thanks in advance