yefj

Advanced Member level 5

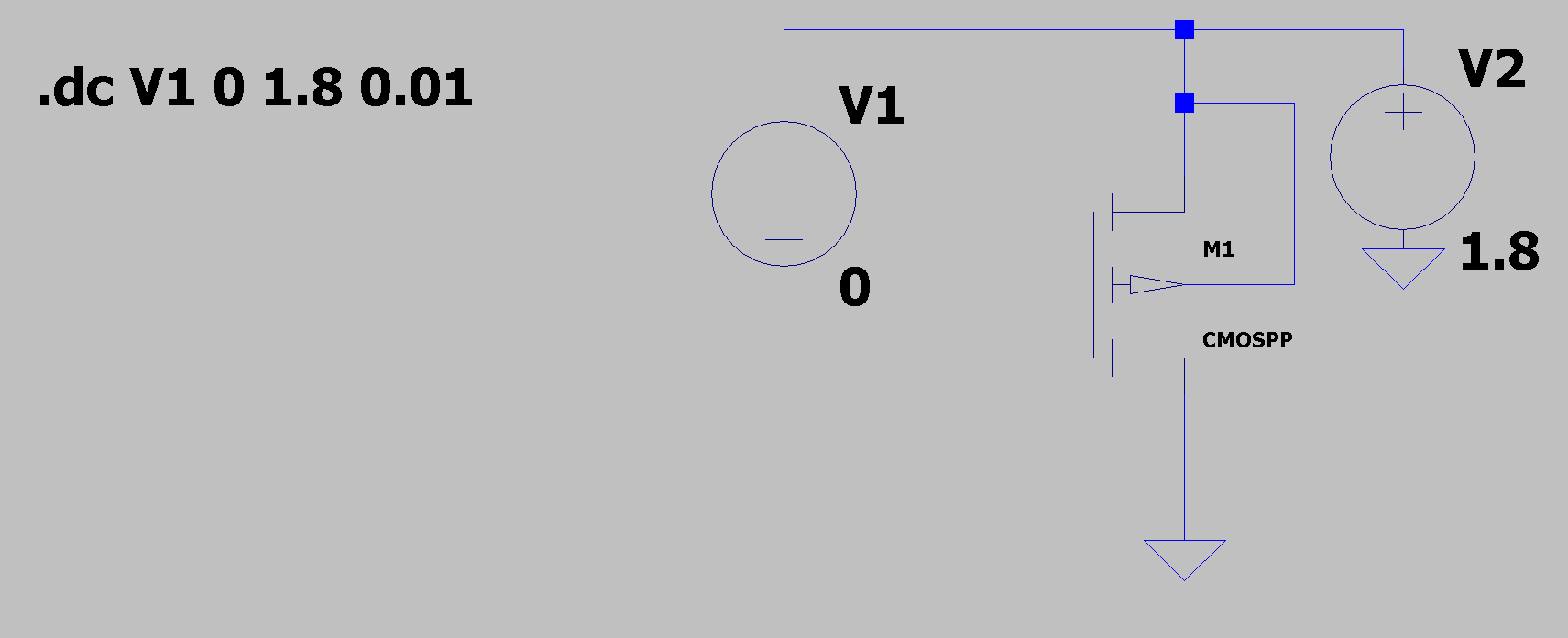

Hello, LTspice is not the real world physics ,Its a netlist thing. I know that NMOS and PMOS have opposite Source location. Generally speaking in real life NMOS and PMOS are simmetric devices and SOURCE and drain are determined by where is the higher voltage. But in LTSPICE i assume its not like in real world  ? in PMOS we can put the VDS voltage source one way and then to reverse its ,unlike real life the Drain and source will not be switched.

? in PMOS we can put the VDS voltage source one way and then to reverse its ,unlike real life the Drain and source will not be switched.

How do i see in LTspice model where is the source of my MOSFET in NMOS and PMOS?

How do i see in LTspice model where is the source of my MOSFET in NMOS and PMOS?