cupoftea

Advanced Member level 6

Hi,

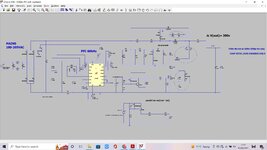

The attached is a 1000W Boost PFC sim in LTspice.......whether either or none of the ringed snubbers is connected up, makes virtually no difference to the voltage peaks on the diode and FET.

Why is this?

The attached is a 1000W Boost PFC sim in LTspice.......whether either or none of the ringed snubbers is connected up, makes virtually no difference to the voltage peaks on the diode and FET.

Why is this?