yefj

Advanced Member level 5

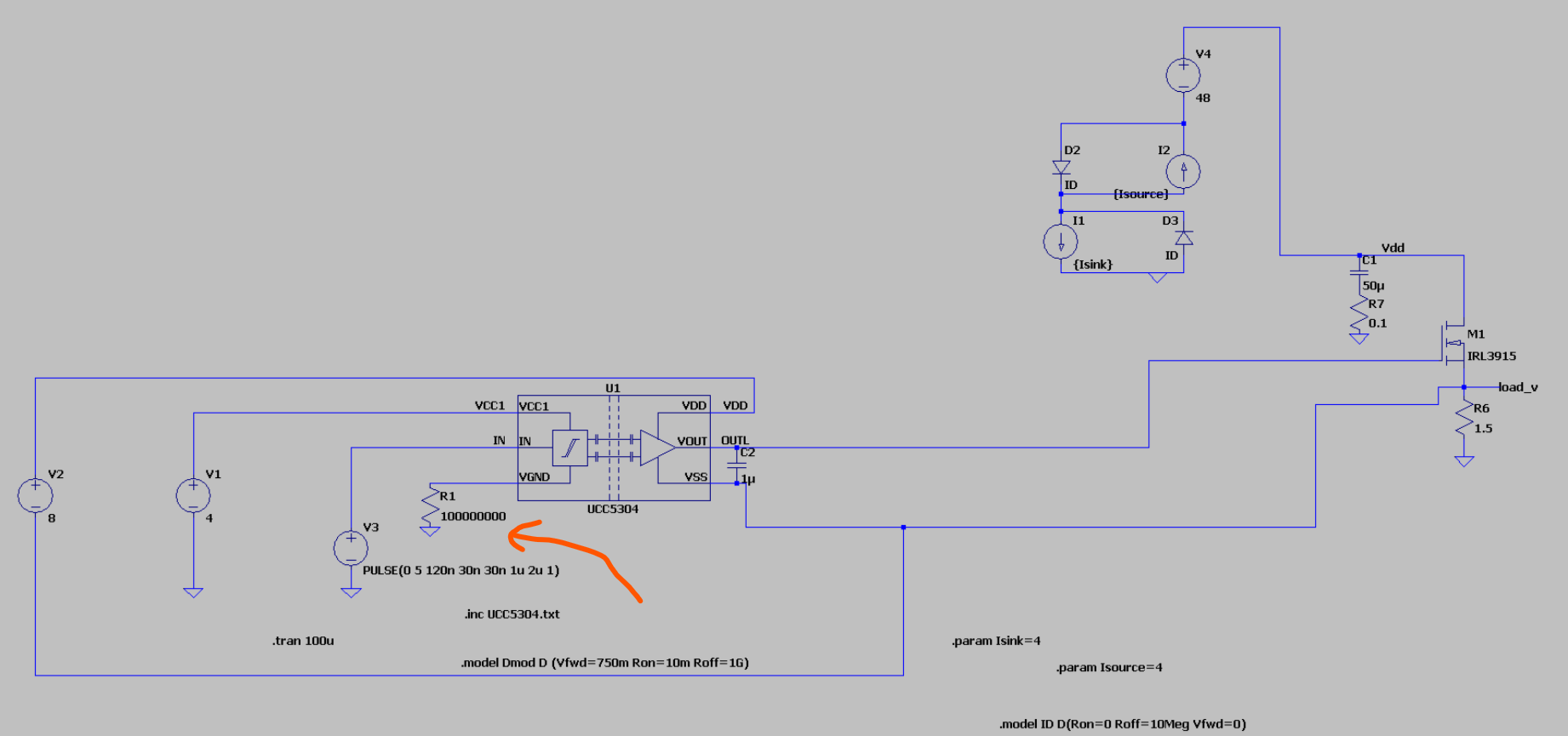

Hello, I have implemented a gate driving of mosfet using UCC5304 as shown below .

I think this is how gate driving is implemented in real life.

However in LTspice its not working .I triem to put 100Mohm to do the floating as shown below.

However the signal is not following the pulse its just charges up and stays there as shown below.

LTspice files are attached.

How to implement this floating driving of a mosfet?

Thansks.

I think this is how gate driving is implemented in real life.

However in LTspice its not working .I triem to put 100Mohm to do the floating as shown below.

However the signal is not following the pulse its just charges up and stays there as shown below.

LTspice files are attached.

How to implement this floating driving of a mosfet?

Thansks.