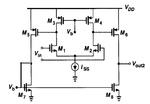

That's a very simple, slow / low bandwidth comparator

and I think you need to consider things like how much

of your jitter budget is allocated to incoming noise,

supply noise etc. and how much to the intrinsic noise

of the comparator.

Low front end gain means more translation of input

voltage noise to output time noise (jitter) across the

trannsfer function slope. Your common mode and

power supply rejection would be improved by more

differential gain up front, you also want this to be

high bandwidth I presume.

You want speed and power consumption to both be

perfect? Good luck.

Insisting that jitter be < 1% of period says to me that

you're not taking error budgeting seriously - or else

somebody else has already eaten all of it.