Paul_V

Newbie level 4

Hello, everyone.

I'm designing a circuit with several LM567 IC's.

It's open-collector output should trigger a logic gate latch and open a lock, once desired frequency is detected.

Using the reference schematic, IC works as expected, turning LED on, when input frequency match.

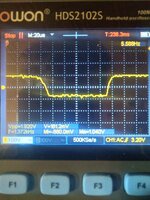

However, when I power-up the circuit, I'm constantly getting a false trigger. LED turns on momentarily.

This is a problem in my design, because it also triggers the latch during power-up, opening a lock.

Tried adding RC, additional pull-up resistor, darlington, input filtering, soft start, etc.

RC does help, but only for a couple of short power-ups and reduces overall sensitivity of the circuit.

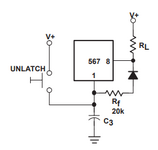

What puzzles me even more, there is a schematic in the datasheet to convert LM567 output to behave as a latch, which also false triggers on power-up.

How can I prevent this power-up trigger?

Thanks a lot in advance.

I'm designing a circuit with several LM567 IC's.

It's open-collector output should trigger a logic gate latch and open a lock, once desired frequency is detected.

Using the reference schematic, IC works as expected, turning LED on, when input frequency match.

However, when I power-up the circuit, I'm constantly getting a false trigger. LED turns on momentarily.

This is a problem in my design, because it also triggers the latch during power-up, opening a lock.

Tried adding RC, additional pull-up resistor, darlington, input filtering, soft start, etc.

RC does help, but only for a couple of short power-ups and reduces overall sensitivity of the circuit.

What puzzles me even more, there is a schematic in the datasheet to convert LM567 output to behave as a latch, which also false triggers on power-up.

How can I prevent this power-up trigger?

Thanks a lot in advance.