mssong

Junior Member level 2

I'm trying to layout a level shifter.

I know the multiple source warning is fine, but the comparison result doesn't make any sense to me.

Is this a guardring issue by any chance?

I'm wondering what other issues I might have.

Additionally, I'm wondering how the level shifter wraps the guardring.

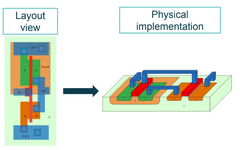

In the following picture, the inside is the pgr guardring and inverter, just outside is the ngr guardring (1.8V), then the next outside is likewise ngr guardring (5V).

Where the ngrs touch each other, the top is 5V and the right is 1.8V.

The layout is clearly correct.

Translated with www.DeepL.com/Translator (free version)

I know the multiple source warning is fine, but the comparison result doesn't make any sense to me.

Is this a guardring issue by any chance?

I'm wondering what other issues I might have.

Additionally, I'm wondering how the level shifter wraps the guardring.

In the following picture, the inside is the pgr guardring and inverter, just outside is the ngr guardring (1.8V), then the next outside is likewise ngr guardring (5V).

Where the ngrs touch each other, the top is 5V and the right is 1.8V.

The layout is clearly correct.

Translated with www.DeepL.com/Translator (free version)