sneha rayala

Junior Member level 2

Hi ,

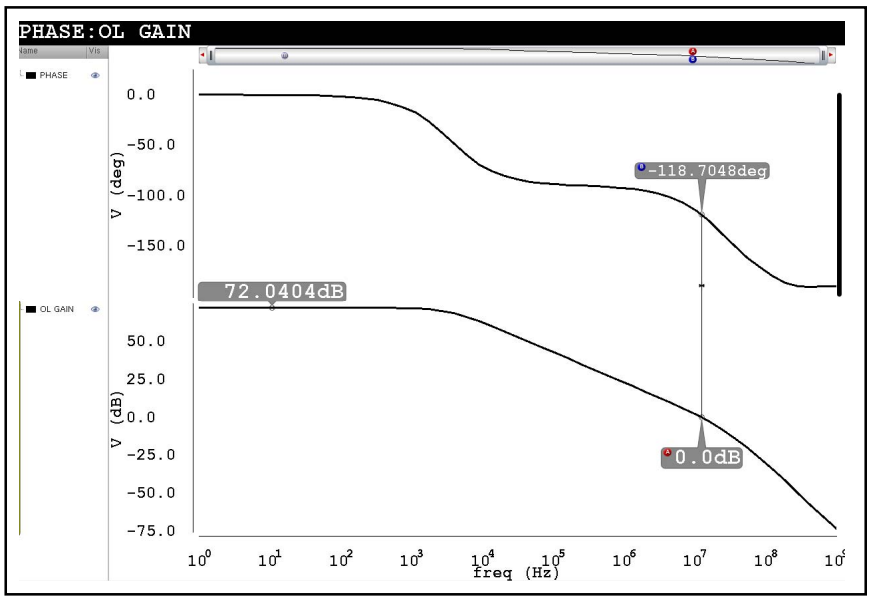

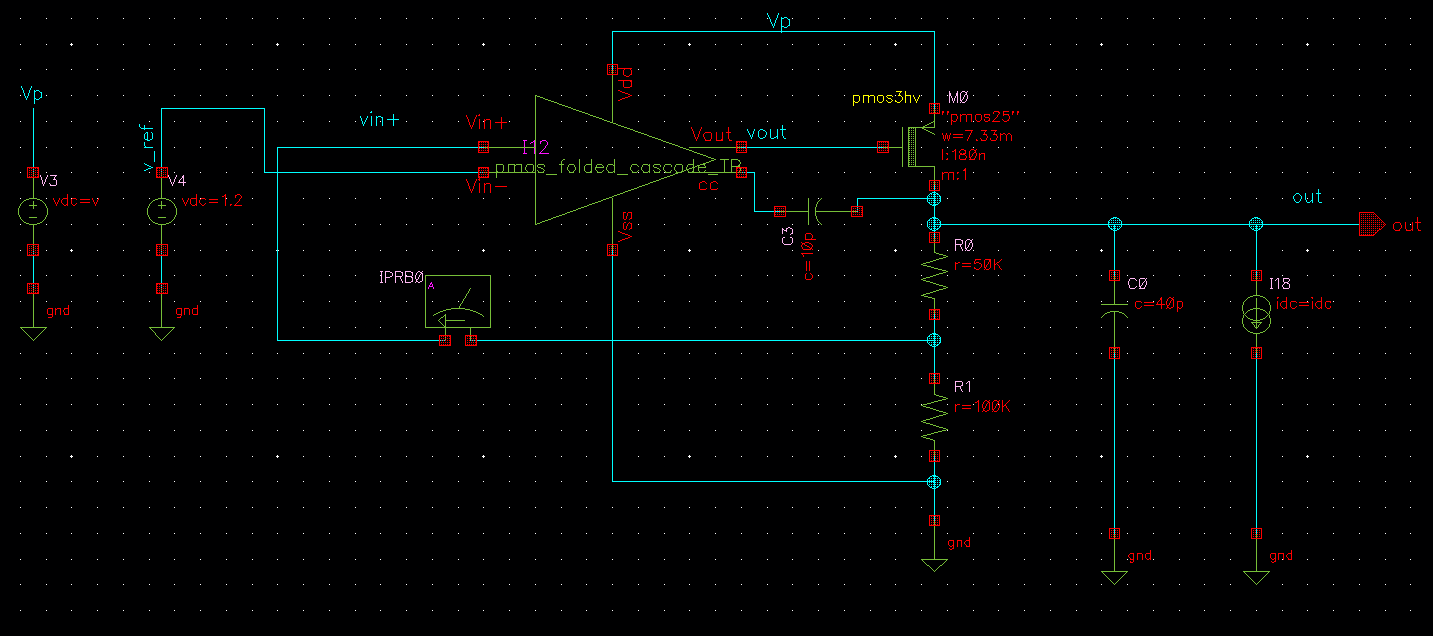

below is the schematic and plot of openloop gain and phase of LDO .

PMOS folded cascode opamp is used as error amplifier , pmos folded cascode gain and phase plots are in BW image 72db gain .

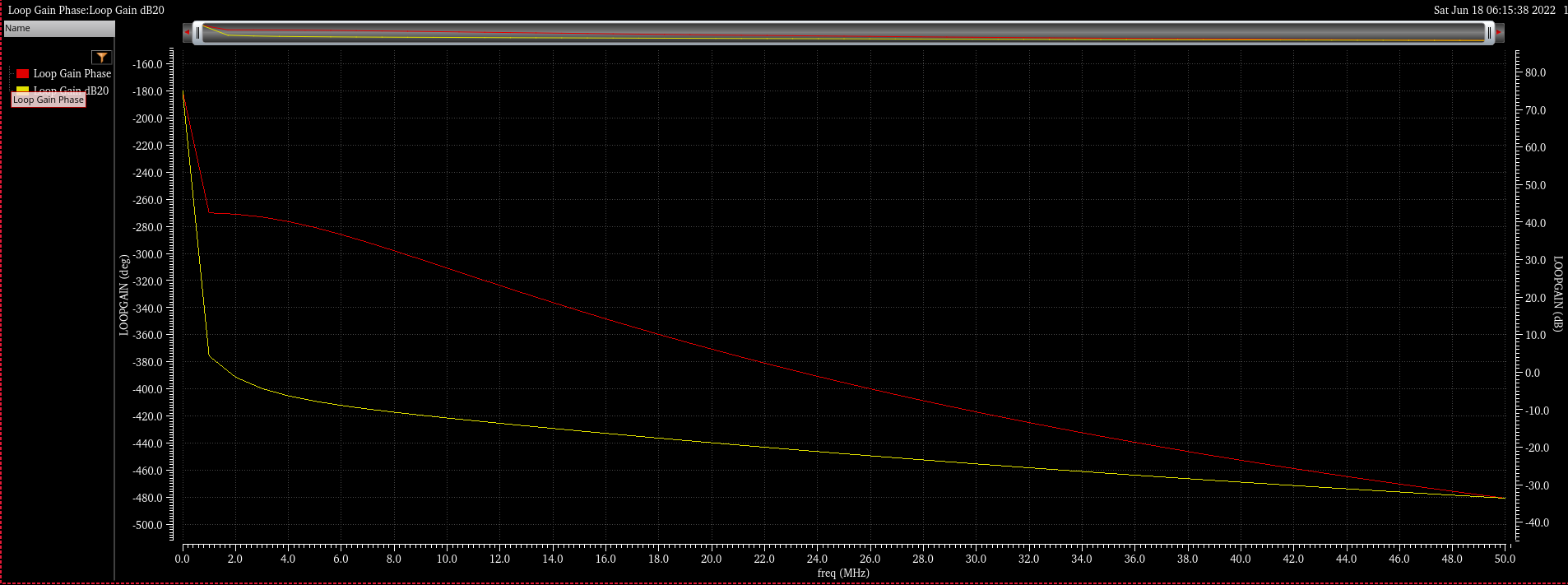

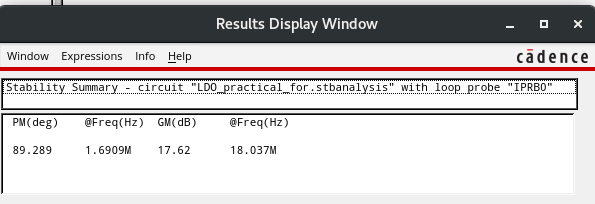

my question here is that in LDO open loop gain plot I see gain dropping from beginning . why is this happening , is it because the pole of error amplifier pushed further towards origin ? if that is the case so for one pole I should see 20db drop in gain per decade but I am seeing lot more than that . I Have also attached stability summary of LDO

below is the schematic and plot of openloop gain and phase of LDO .

PMOS folded cascode opamp is used as error amplifier , pmos folded cascode gain and phase plots are in BW image 72db gain .

my question here is that in LDO open loop gain plot I see gain dropping from beginning . why is this happening , is it because the pole of error amplifier pushed further towards origin ? if that is the case so for one pole I should see 20db drop in gain per decade but I am seeing lot more than that . I Have also attached stability summary of LDO

Last edited: