nithinp

Junior Member level 2

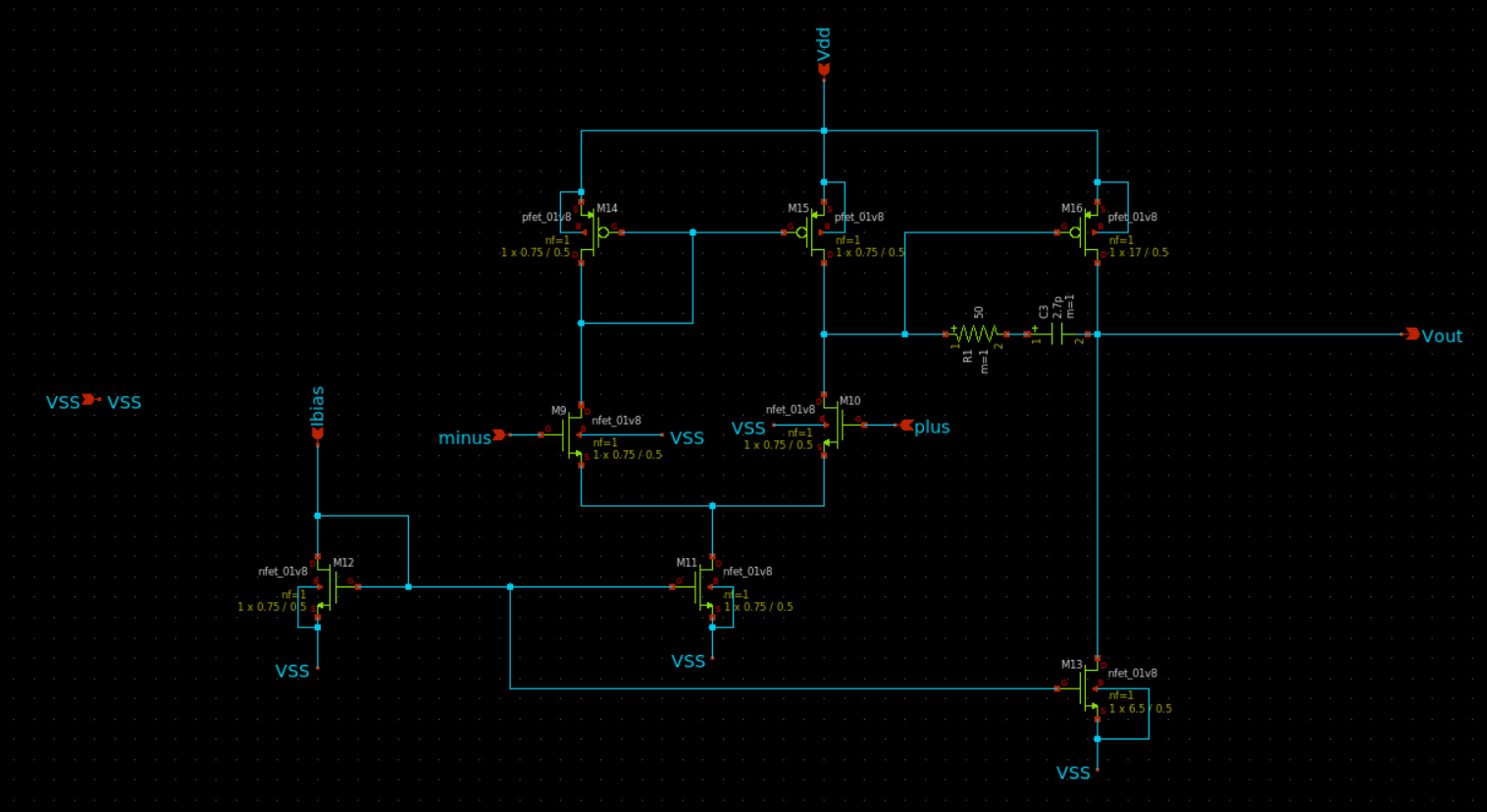

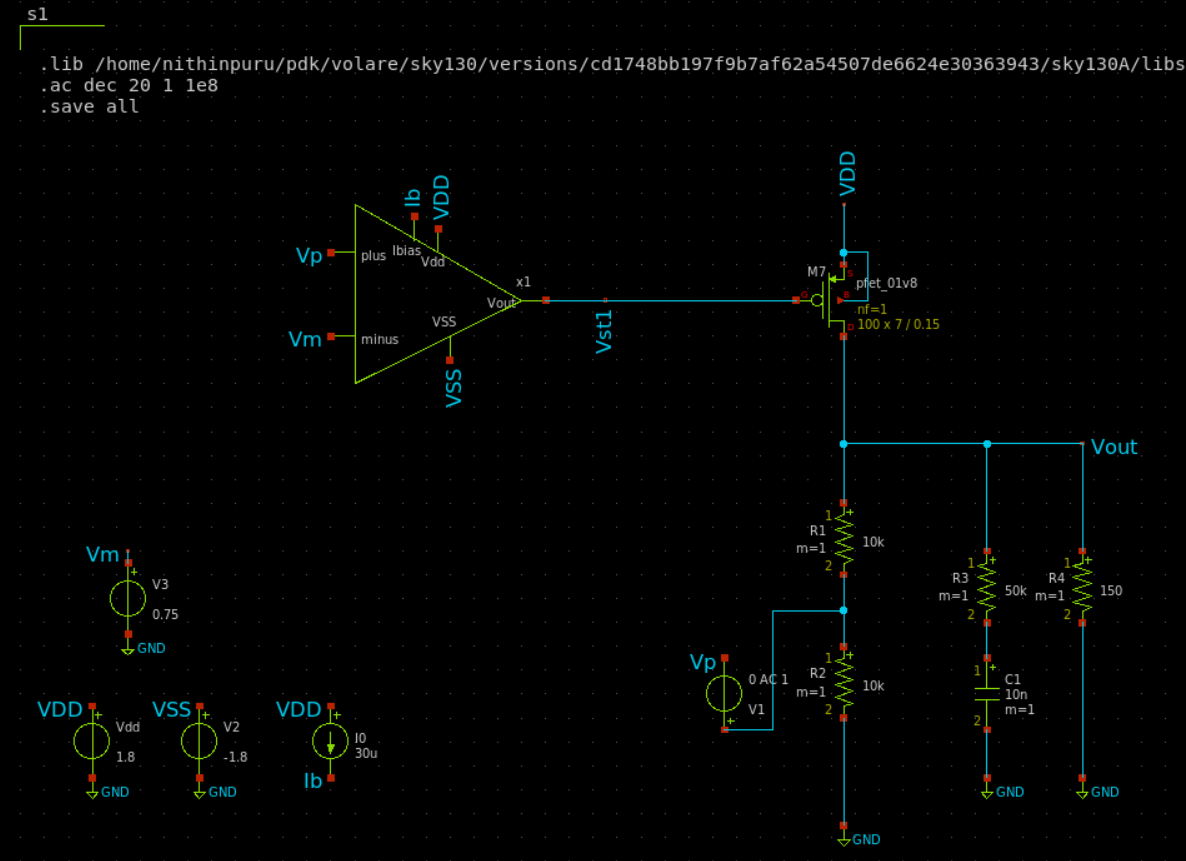

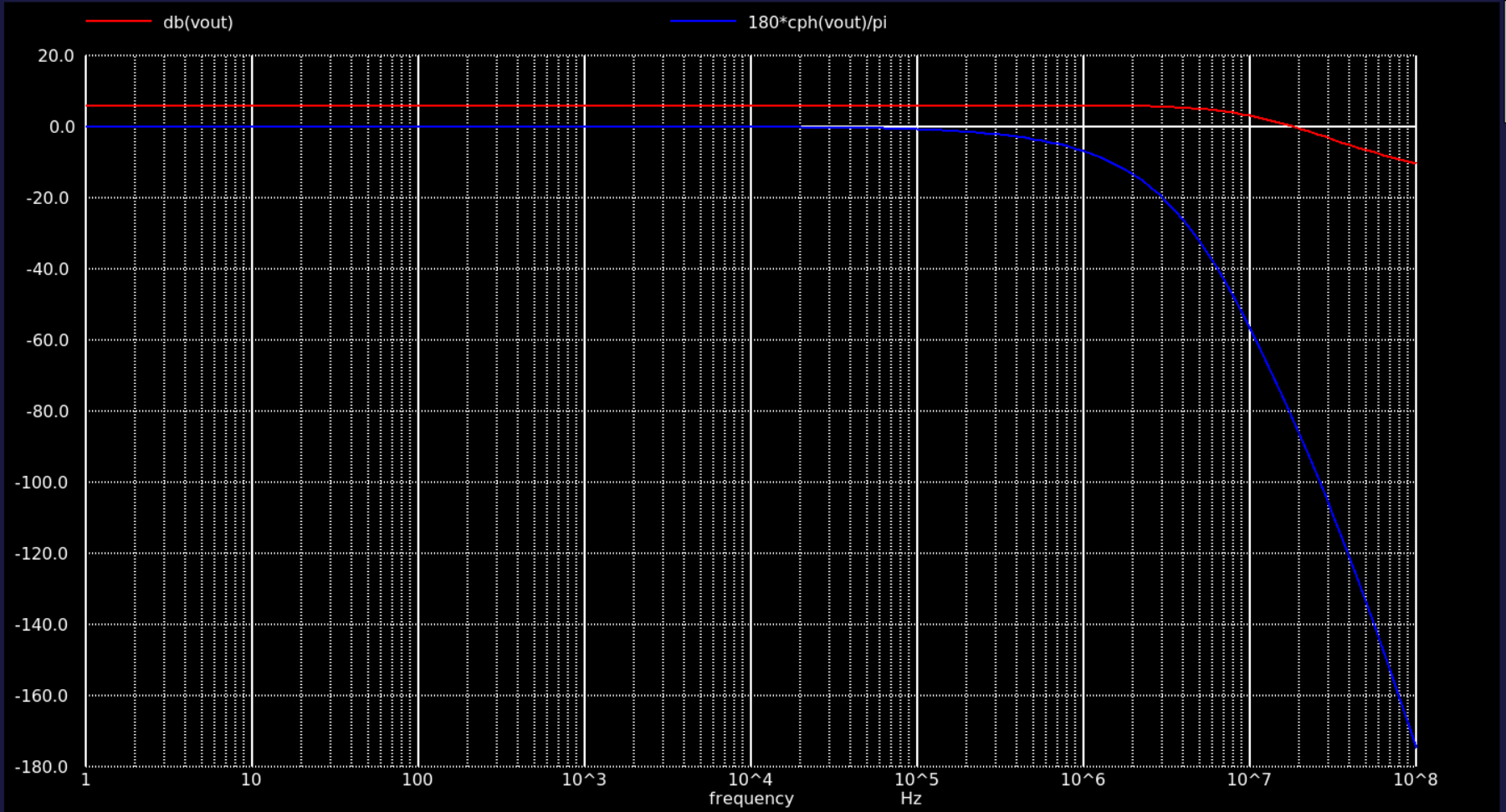

I'm designing an LDO with SKY130PDK for Vreg=1.5, Vdd=1.8, Ilaod=1mA-10mA Vref=0.75. I used a 2 stage OTA I built earlier which provides a gain of 60dB and phase margin of 80deg but when I try LDO design , I get a regulated voltage of 1.5V but my gain is messes up like 6dB, I know I'm having problem with pole compensation. Please help