NIDHINDAS

Newbie level 6

Hello,

PFA for the design using FAN-7392 to drive dual supply power with the dual load(battery) connected in series (+.........-+..........- ).

The microcontroller is PIC16F877A with separate Two PWM driving positive side and negative side MOSFET independently.

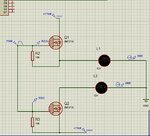

MCUs ground is -17 volt, not 0 of dual supply, to measure -ve volt as positive.

The issue is Q1 is not conducting now, what may be the reasons?

Q2 is working now.

2. MCUs can't measure -ve voltages how this is taken care of in the situation it needs.

Thanks in advance.

Regards,

Nidhindas

PFA for the design using FAN-7392 to drive dual supply power with the dual load(battery) connected in series (+.........-+..........- ).

The microcontroller is PIC16F877A with separate Two PWM driving positive side and negative side MOSFET independently.

MCUs ground is -17 volt, not 0 of dual supply, to measure -ve volt as positive.

The issue is Q1 is not conducting now, what may be the reasons?

Q2 is working now.

2. MCUs can't measure -ve voltages how this is taken care of in the situation it needs.

Thanks in advance.

Regards,

Nidhindas