tiredstudent

Newbie

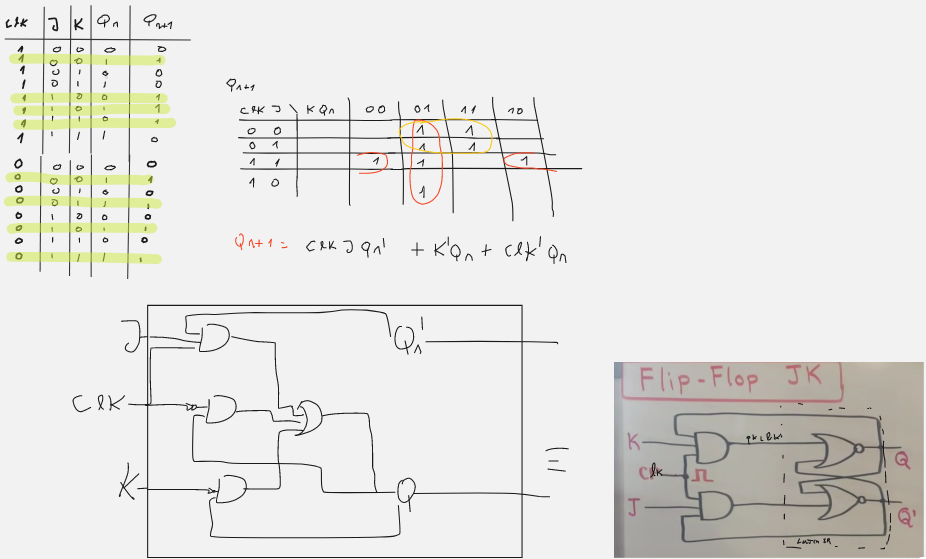

I'm getting started in digital electronics and I've never seen an implementation of a flip flop JK like the one I did. I know its not optimal, but is it ok? the NAND version and the one using a latch SR are not easy to came up with for me. I feel like I need to just remember them, while this implemetation is easy to get when you know how the FF works