Osawa_Odessa

Banned

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

My intention is that nothing is connected to the output. Can you explain it in detail? Because it seems that Ids = I = const always!Even with nothing connected to Vout, it will not always be in saturation. In fact, for any given current, you will have to choose Vgs very carefully to get it into saturation.

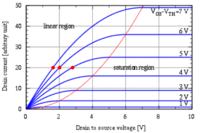

Ids is constant, but that doesn't mean the MOSFET is in saturation. When Vgs changes, Vds will change, but for a wide range of Vgs the MOSFET will be in the linear region.Because it seems that Ids = I = const always!

Here's some idealized curves (swiped from Wikipedia). Consider what happens if Ids is set to 20 units and Vgs is varied.Can you explain it in detail?

that is if current source is 20 units,if current source is 50 units & if output is open,then it has to be in saturation right?