e-music

Member level 5

Interfacing STM32F429 (FMC) with a 1 GBit Parallel NOR Flash (M29EWL)

Hello Folks!

I'm trying to interface a 1 GBit parallel NOR flash with an STM32F429 microcontroller through the FMC peripheral. The full part number is: JS28F00AM29EWLA. Here is the datasheet: View attachment m29ew_256mb_2gb.pdf

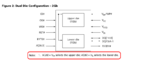

The problem is, the 256 MB (2 Gbit) address space dedicated to the first bank of the FMC peripheral for the NOR/SRAM memories is divided across 4 sub banks, 64 MB each with an individual NEx (chip select) signal for each sub-bank.

As I can see, STM32CubeMX has no problem configuring a single sub-bank with 26 address bits. However, accessing any memory space beyond the first 64 MB causes a Hard Fault interrupt if the corresponding sub-bank has not been enabled earlier.

Addressing for such a device is a little bit confusing for me. From the datasheet of the M29EWL, it says 25 address lines are enough to address up to, but not above, 1 GBit of memory space. Could someone explain it for me? Could it be because the memory is made of "uniform blocks of 128 KB each" so the address lines needed are much less than those needed on other devices?

Thank you in advance!

Hello Folks!

I'm trying to interface a 1 GBit parallel NOR flash with an STM32F429 microcontroller through the FMC peripheral. The full part number is: JS28F00AM29EWLA. Here is the datasheet: View attachment m29ew_256mb_2gb.pdf

The problem is, the 256 MB (2 Gbit) address space dedicated to the first bank of the FMC peripheral for the NOR/SRAM memories is divided across 4 sub banks, 64 MB each with an individual NEx (chip select) signal for each sub-bank.

As I can see, STM32CubeMX has no problem configuring a single sub-bank with 26 address bits. However, accessing any memory space beyond the first 64 MB causes a Hard Fault interrupt if the corresponding sub-bank has not been enabled earlier.

Addressing for such a device is a little bit confusing for me. From the datasheet of the M29EWL, it says 25 address lines are enough to address up to, but not above, 1 GBit of memory space. Could someone explain it for me? Could it be because the memory is made of "uniform blocks of 128 KB each" so the address lines needed are much less than those needed on other devices?

Thank you in advance!