Jordon

Member level 1

- Joined

- Dec 25, 2022

- Messages

- 33

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Shanghai, China

- Activity points

- 265

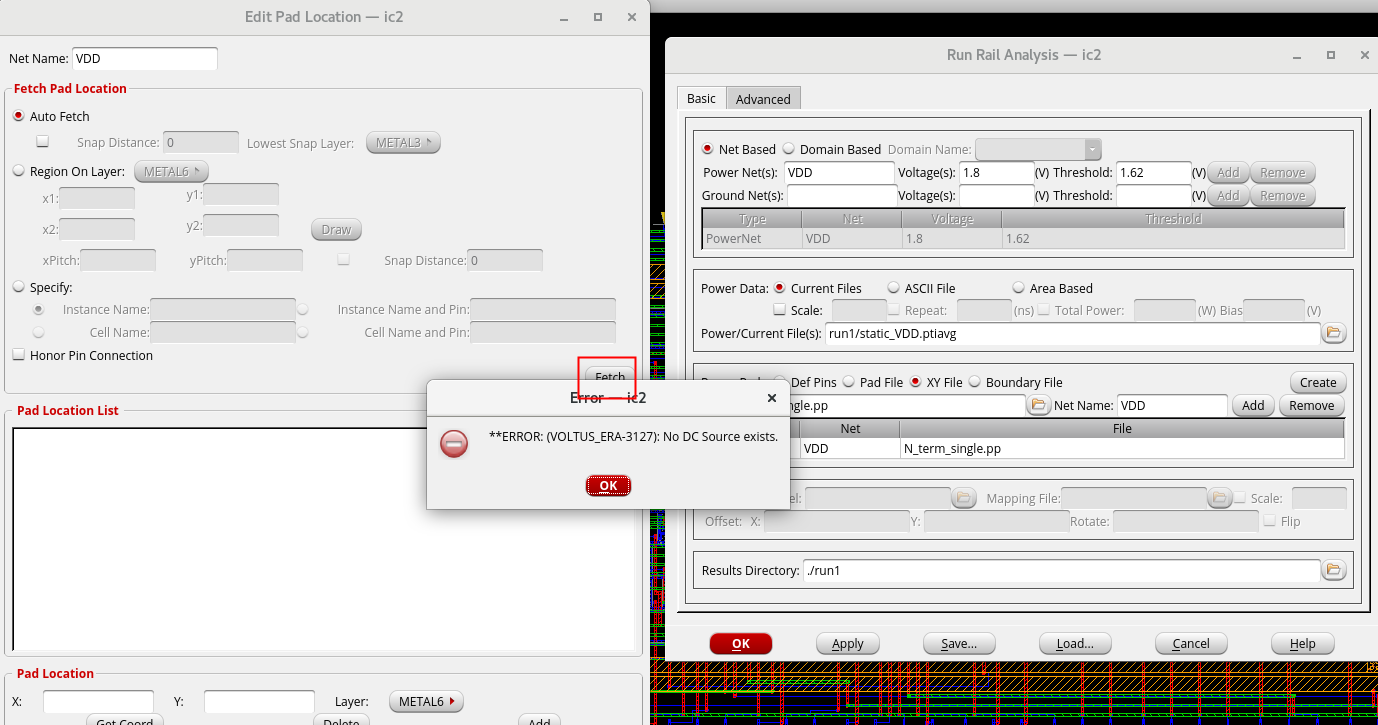

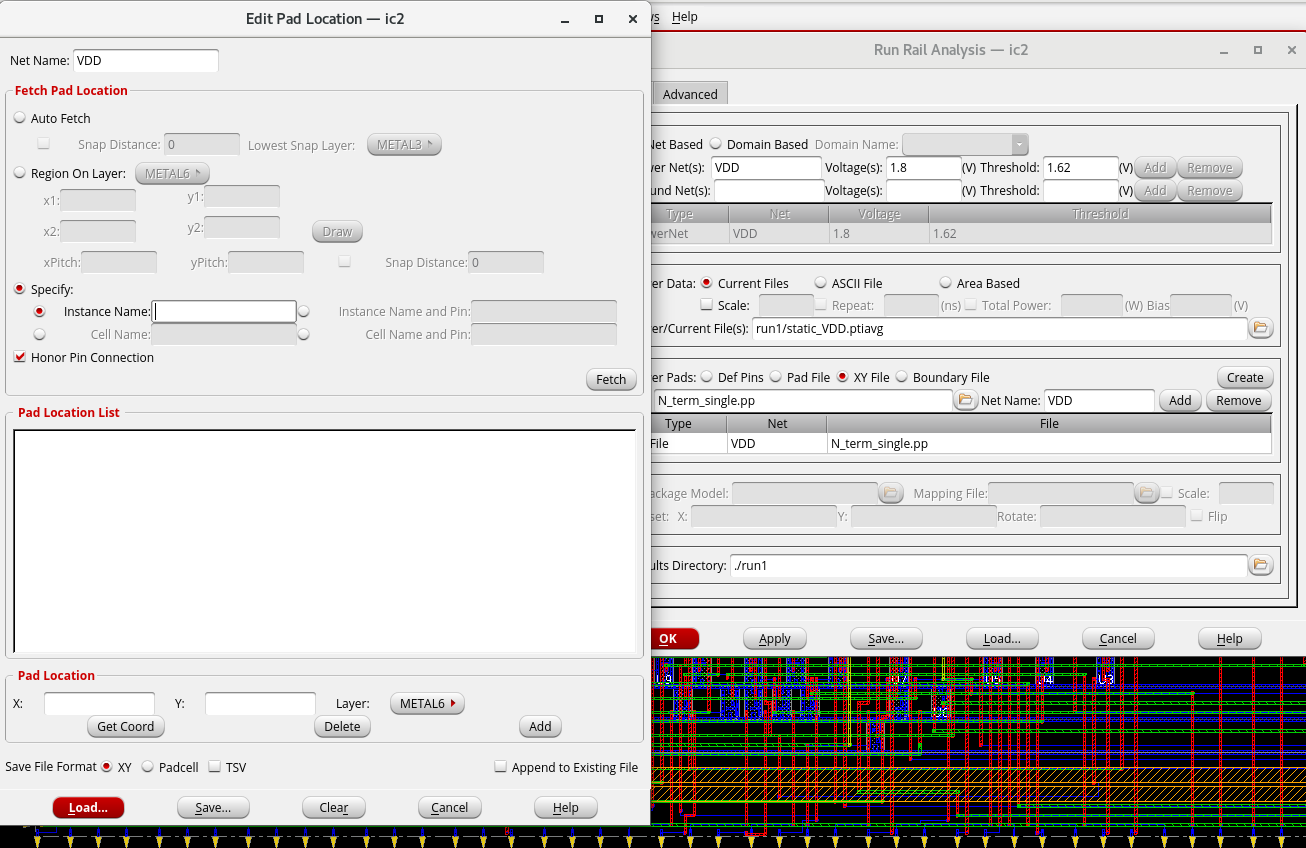

Hi, when i try to run rail analysis, it need a XY file, but i cannot create a XY file as tutorials, tap 'create', the Pad location list is empty, what is the possible reason? in thr tutorial, the pad location list has two items:VDD and VSS, but mine is not.

Thank you.

Thank you.