electronics_rama

Member level 3

Hi,

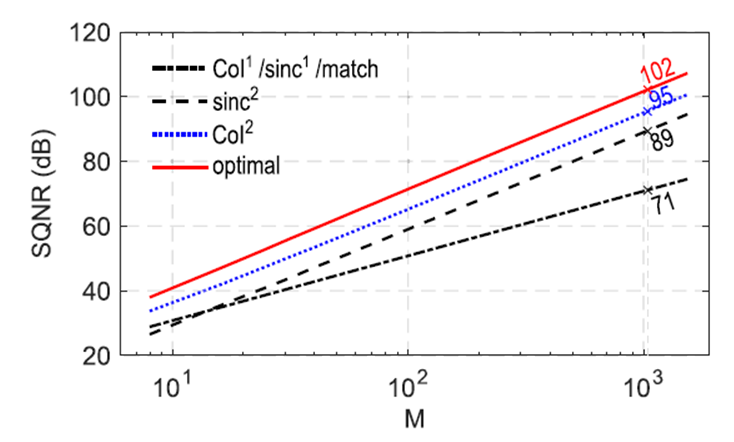

I am referring to a paper for the optimum filtering which can be used for the incremental delta-sigma ADC. I came across a below point and below is the diagram stating that for a given sigma-delta modulator loop, we can achieve higher and higher dynamic range by using higher and higher order filters. M is the OSR in the below diagram. Col1 is the first order filter. Col2 is the second order filter. By using Col2, the dynamic range is extended by 24dB. If this is true, why do we have to go for higher order delta sigma modulator? We can use a first-order modulator and higher-order filter to achieve a high-resolution ADC. Can anyone explain this?

Thanks

I am referring to a paper for the optimum filtering which can be used for the incremental delta-sigma ADC. I came across a below point and below is the diagram stating that for a given sigma-delta modulator loop, we can achieve higher and higher dynamic range by using higher and higher order filters. M is the OSR in the below diagram. Col1 is the first order filter. Col2 is the second order filter. By using Col2, the dynamic range is extended by 24dB. If this is true, why do we have to go for higher order delta sigma modulator? We can use a first-order modulator and higher-order filter to achieve a high-resolution ADC. Can anyone explain this?

Thanks