wonderfulnx

Newbie

- Joined

- Sep 10, 2023

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- Beijing, China

- Activity points

- 93

Hi everyone, I've been trying to measure and use some EPCOS SAW Filters recently and found something strange with their impedance matching network. This strange point exists in many of their models and here I'm using the model "B39321B3741H110" as the example. I've attached the datasheet and the Impedance matching application note they provided below.

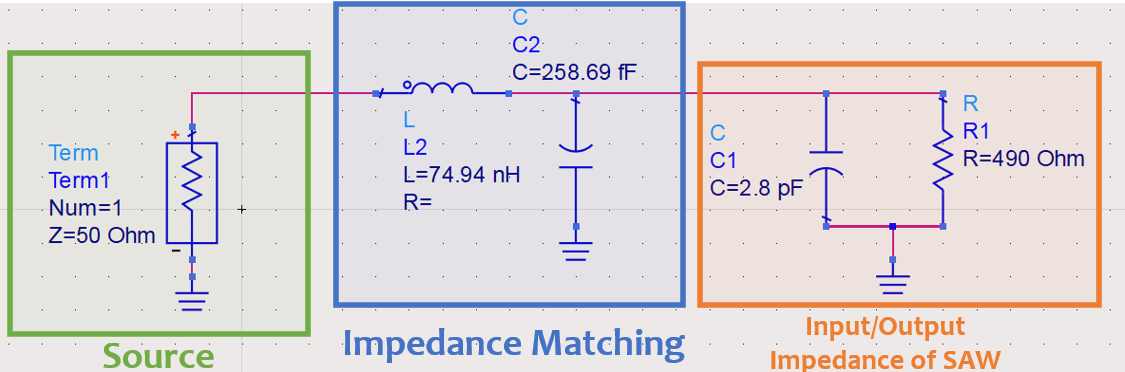

This SAW filter requires input and output matching at the same time. According to the datasheet, the impedance on both input and output ports (based on an ideal matching) is a 490 Ohm resistor in parallel with a 2.8pF capacitor (490 Ohm || 2.8 pF). In order to match a 50-ohm source/load, a simple LC matching is used as shown (center frequency 315Mhz).

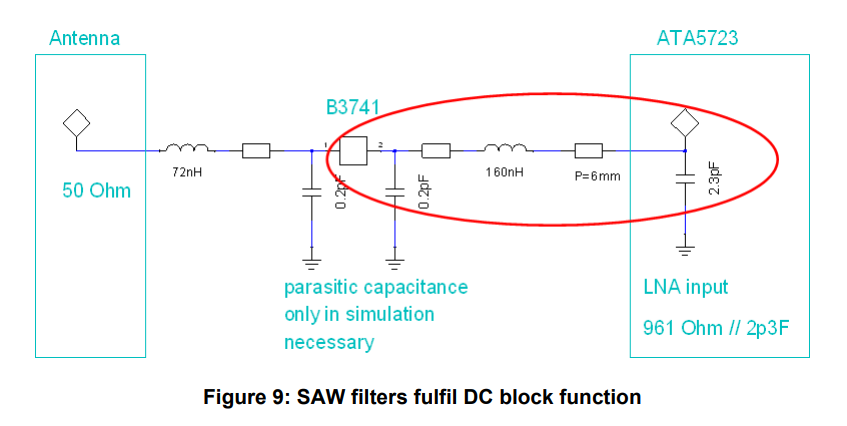

This matching network is consistent with the schematic given in application note 18 on page 11, where a 72nH inductor is used (not 74nH, probably considering the parasitic inductance of the PCB itself), as shown:

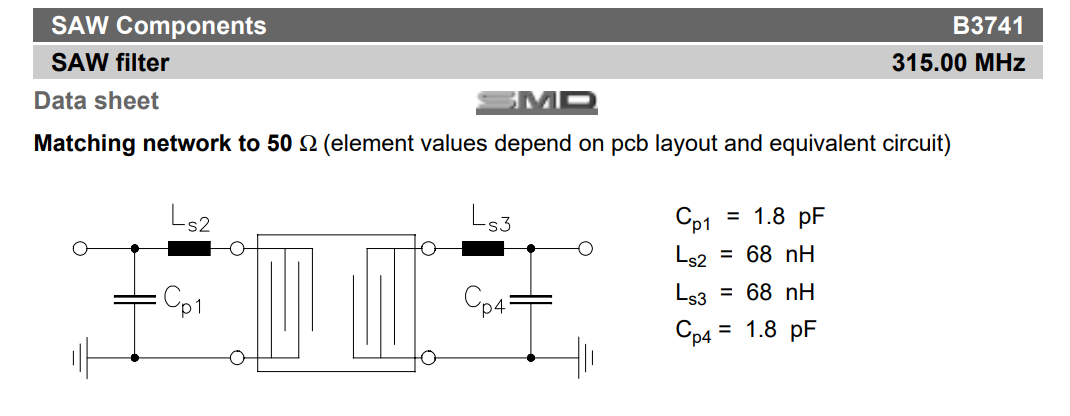

The 0.2pF capacitance is said to be considered only in simulation so I guess no need for them in actual PCB. But here comes the strange thing, the datasheet of this component clearly shows a matching network as this:

where the 0.2pF capacitor (close to the SAW) is gone and the series inductance continues to reduce to 68nH. And there is another capacitor in parallel that is close to the 50-ohm source. So why is there a 1.8pF capacitor here? Its purpose is not to substitute the 0.2pF one since they aren't in the same location. And it does not help the impedance matching here I think......

Also, How much is the typical value of parasitic inductance on a PCB, should the series inductance continue to reduce like this?

BTW, the suggested layout for this matching network is this:

This SAW filter requires input and output matching at the same time. According to the datasheet, the impedance on both input and output ports (based on an ideal matching) is a 490 Ohm resistor in parallel with a 2.8pF capacitor (490 Ohm || 2.8 pF). In order to match a 50-ohm source/load, a simple LC matching is used as shown (center frequency 315Mhz).

This matching network is consistent with the schematic given in application note 18 on page 11, where a 72nH inductor is used (not 74nH, probably considering the parasitic inductance of the PCB itself), as shown:

The 0.2pF capacitance is said to be considered only in simulation so I guess no need for them in actual PCB. But here comes the strange thing, the datasheet of this component clearly shows a matching network as this:

where the 0.2pF capacitor (close to the SAW) is gone and the series inductance continues to reduce to 68nH. And there is another capacitor in parallel that is close to the 50-ohm source. So why is there a 1.8pF capacitor here? Its purpose is not to substitute the 0.2pF one since they aren't in the same location. And it does not help the impedance matching here I think......

Also, How much is the typical value of parasitic inductance on a PCB, should the series inductance continue to reduce like this?

BTW, the suggested layout for this matching network is this: