Khashia

Member level 1

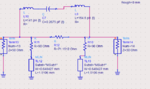

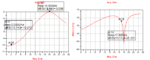

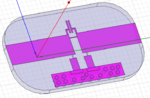

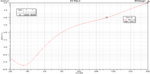

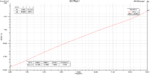

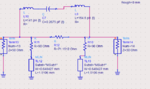

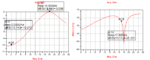

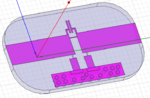

we have a gain equalizer designed using Mellor topology however here, lumped reactive elements are replaced by microstrip components. The design as originally designed in ADS software has very good return loss and slope/freq response. However when the same equalizer is implemented through microstrip elements and simulated in HFSS, it needed optimization and tweaking in microstrip dimensions. The final design gives S21 response as required but the S11 return loss is very poor.

What could be the possible reason and how to improve this return loss? Note that microstrip lines at both ports are nominal 50 ohm characteristic impedance lines designed.

- - - Updated - - -

The S11 is below 10 dB only upto 13.1 GHz, if this GEQ is inserted into the system chain how useful could it prove? provided it has around -4dB insertion loss (in addition to 10 dB attenuation slope) and poor return loss.

What could be the possible reason and how to improve this return loss? Note that microstrip lines at both ports are nominal 50 ohm characteristic impedance lines designed.

- - - Updated - - -

The S11 is below 10 dB only upto 13.1 GHz, if this GEQ is inserted into the system chain how useful could it prove? provided it has around -4dB insertion loss (in addition to 10 dB attenuation slope) and poor return loss.