Calltronics

Newbie

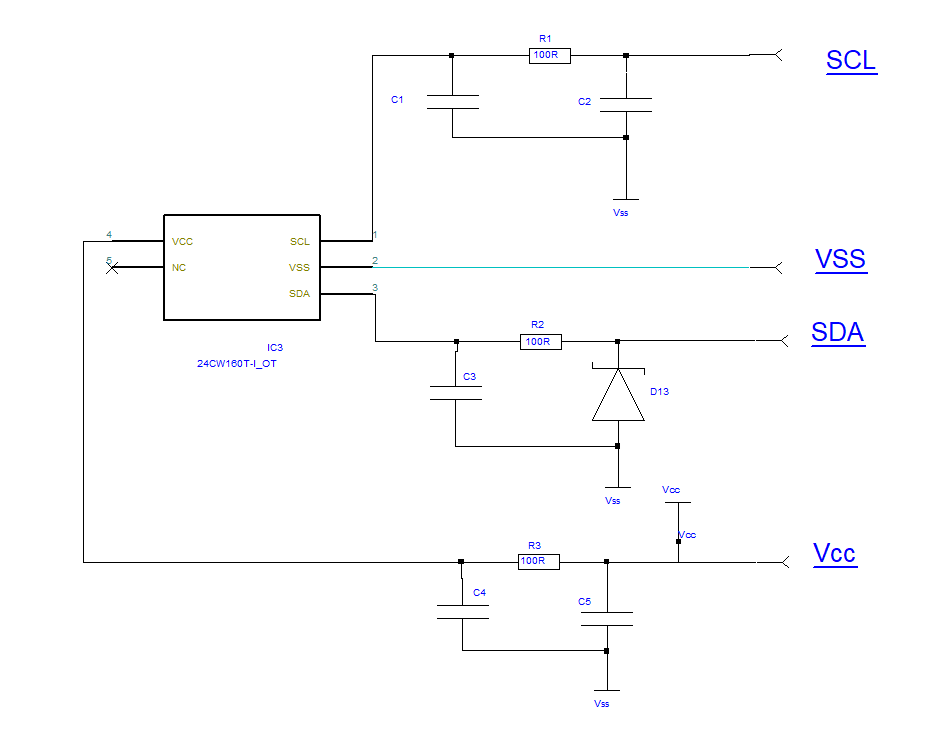

I have to reverse engineer this interface to the microchip memory.

Anyone shed anylight on the value of the Zener.

Also the capacitors.

Appreciate your help

Anyone shed anylight on the value of the Zener.

Also the capacitors.

Appreciate your help