crumpet

Newbie level 4

- Joined

- Aug 21, 2010

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Location

- San Francisco

- Activity points

- 1,320

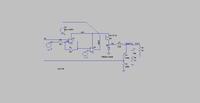

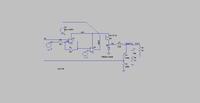

I'm trying to simulate a purely hysteretic converter in LTSpice (no one-shots used).

I used an Op-Amp block w feedback resistors to make a hysteretic comparator, the hysteresis is about 20mV.

The OpAmp drives a PMOS and 0.4V shottky is used for the catch-diode.

On VOUT there is inductor and cap and feedback resistors provide divided version of output voltage back to the hyst-comparator.

When I sumulate this circuit, I see huge ripple (200mV to 1V) on the output under most loads.

I tried varying the capacitor and inductor values (1uH-10uH, 2uF-100uF) with minimal improvements.

The lowest I could get the ripple to drop was 80mVpp when load current was reduced to smaller range.

(see attached screen captures)

Do you know what I could be doing wrong?

I used an Op-Amp block w feedback resistors to make a hysteretic comparator, the hysteresis is about 20mV.

The OpAmp drives a PMOS and 0.4V shottky is used for the catch-diode.

On VOUT there is inductor and cap and feedback resistors provide divided version of output voltage back to the hyst-comparator.

When I sumulate this circuit, I see huge ripple (200mV to 1V) on the output under most loads.

I tried varying the capacitor and inductor values (1uH-10uH, 2uF-100uF) with minimal improvements.

The lowest I could get the ripple to drop was 80mVpp when load current was reduced to smaller range.

(see attached screen captures)

Do you know what I could be doing wrong?