zzzhhh

Newbie level 5

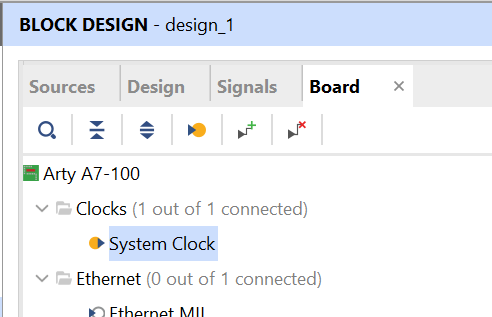

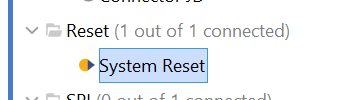

There are two board components on the Digilent Arty A7-100T FPGA development board: System Reset and System Clock, as shown in the board file board.xml:

The System Reset is so easy to use: it automatically shows up in the Block Design diagram and get configured. I don't need to modify the Arty-A7-100-Master.xdc file. Actually, I don't even know where this reset signal comes from. But the use of System Clock is a nightmare. I insert it into the Block Design diagram by manually drag-and-drop it from the board tab. Vivado then forces me to add a Clocking Wizard IP and the icon to the left of System Clock turns orange, like the screenshot above shows. Vivado gives the port a name "sys_clock" as defined in board file board.xml. But if I remove the Clocking Wizard IP because I don't need it, this icon turns white meaning that the System Clock board component is not connected. Now the port sys_clock is a common signal and I have to specify its physical pin connection in Arty-A7-100-Master.xdc file. That works but that's not what I want, so I have to keep the Clocking Wizard IP and run Validate Design -> Synthesis -> Run Implementation -> Generate Bitstream, But I get a long error at the bitstream generation step:

The settings in Arty-A7-100-Master.xdc file does not apply. I'm guessing that's for common signal when I delete the Clocking Wizard IP. Then, I obey the suggestion in the error message by using "set_property SEVERITY {Warning} [get_drc_checks UCIO-1]" command. First I run this command in Tcl Console. Vivado add some garbage in the Arty-A7-100-Master.xdc file but still report the same error. So I add this command in Arty-A7-100-Master.xdc file and thank goodness the bitstream is generated successfully.

But I'm unhappy because I was at first expecting that the use of System Clock board component should be as easy as System Reset. Their entries in either board file and Vivado Board tab are so similar, so why are their usage so different? Specifically, I have the following questions:

1) How to add the System Clock board component without adding Clocking Wizard IP? Even if I connect sys_clock port to some other parts, the icon is white. The System Reset (named "reset") does not require any additional IP core for it to be added into the Block Design diagram.

2) The System Reset does not incur the error message which asks for a specification of FPGA chip pin, but why does sys_clock want it, and why does reset not want it? What's the difference of these two board components?

3) If I have to specify FPGA chip pin to connect to sys_clock, how to do it? I tried uncommenting the following statements in Arty-A7-100-Master.xdc file:

4) Why the command suggested in the error message does not work in Tcl Console, but I have to add it in the Arty-A7-100-Master.xdc file?

5) How to use the System Clock on Digilent Arty A7-100T in a way as easy as System Reset? I still think sys_clock should be used as easy as reset. What's the difference? If Digilent can make reset so easy to use, it should make sys_clock all the same easy to use too, say, it can be added automatically by auto-connect function in Block Design diagram, there is no need to add Clocking Wizard, there is no need to edit Arty-A7-100-Master.xdc file like reset, and there is no need to add that abstruse command in the xdc file.

I'm using Vivado 2023.1 on Windows 10. Thanks in advance for your (to-the-point) answer.

and Board tab in Vivado:<component name="reset" display_name="System Reset" type="chip" sub_type="system_reset" major_group="Reset">

<description>CPU Reset Push Button, active low</description>

</component>

<component name="sys_clock" display_name="System Clock" type="chip" sub_type="system_clock" major_group="Clocks">

<description>3.3V Single-Ended 100MHz oscillator used as system clock on the board</description>

</component>

The System Reset is so easy to use: it automatically shows up in the Block Design diagram and get configured. I don't need to modify the Arty-A7-100-Master.xdc file. Actually, I don't even know where this reset signal comes from. But the use of System Clock is a nightmare. I insert it into the Block Design diagram by manually drag-and-drop it from the board tab. Vivado then forces me to add a Clocking Wizard IP and the icon to the left of System Clock turns orange, like the screenshot above shows. Vivado gives the port a name "sys_clock" as defined in board file board.xml. But if I remove the Clocking Wizard IP because I don't need it, this icon turns white meaning that the System Clock board component is not connected. Now the port sys_clock is a common signal and I have to specify its physical pin connection in Arty-A7-100-Master.xdc file. That works but that's not what I want, so I have to keep the Clocking Wizard IP and run Validate Design -> Synthesis -> Run Implementation -> Generate Bitstream, But I get a long error at the bitstream generation step:

[DRC UCIO-1] Unconstrained Logical Port: 1 out of 52 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: sys_clock.

The settings in Arty-A7-100-Master.xdc file does not apply. I'm guessing that's for common signal when I delete the Clocking Wizard IP. Then, I obey the suggestion in the error message by using "set_property SEVERITY {Warning} [get_drc_checks UCIO-1]" command. First I run this command in Tcl Console. Vivado add some garbage in the Arty-A7-100-Master.xdc file but still report the same error. So I add this command in Arty-A7-100-Master.xdc file and thank goodness the bitstream is generated successfully.

But I'm unhappy because I was at first expecting that the use of System Clock board component should be as easy as System Reset. Their entries in either board file and Vivado Board tab are so similar, so why are their usage so different? Specifically, I have the following questions:

1) How to add the System Clock board component without adding Clocking Wizard IP? Even if I connect sys_clock port to some other parts, the icon is white. The System Reset (named "reset") does not require any additional IP core for it to be added into the Block Design diagram.

2) The System Reset does not incur the error message which asks for a specification of FPGA chip pin, but why does sys_clock want it, and why does reset not want it? What's the difference of these two board components?

3) If I have to specify FPGA chip pin to connect to sys_clock, how to do it? I tried uncommenting the following statements in Arty-A7-100-Master.xdc file:

but it does not work, perhaps because it is only for common signals, not for the special System Clock board component even though its name is also sys_clock.## Clock signal

set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports { sys_clock }]; #IO_L12P_T1_MRCC_35 Sch=gclk[100]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports { sys_clock }];

4) Why the command suggested in the error message does not work in Tcl Console, but I have to add it in the Arty-A7-100-Master.xdc file?

5) How to use the System Clock on Digilent Arty A7-100T in a way as easy as System Reset? I still think sys_clock should be used as easy as reset. What's the difference? If Digilent can make reset so easy to use, it should make sys_clock all the same easy to use too, say, it can be added automatically by auto-connect function in Block Design diagram, there is no need to add Clocking Wizard, there is no need to edit Arty-A7-100-Master.xdc file like reset, and there is no need to add that abstruse command in the xdc file.

I'm using Vivado 2023.1 on Windows 10. Thanks in advance for your (to-the-point) answer.