melkord

Full Member level 3

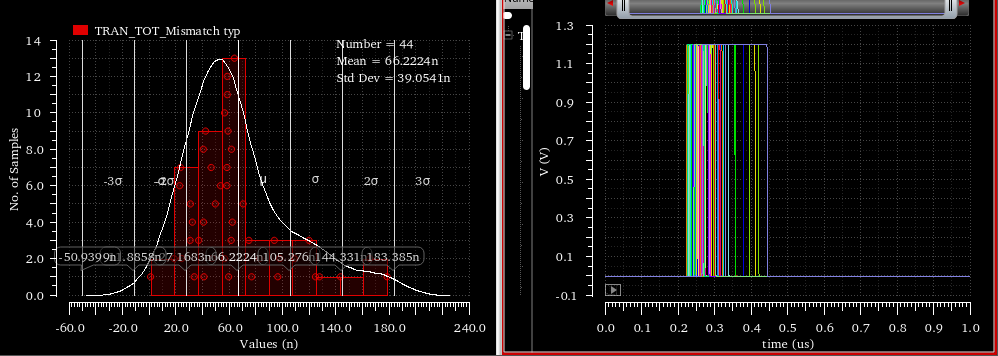

The way I did it currently is by looking for the DAC code that results a ToT that is the closest with the ToT at nominal simulation.

It catches 44 out of 50 samples, but I keep getting very high standard deviation even though I have already made my circuit larger.

How to simulate it correctly?

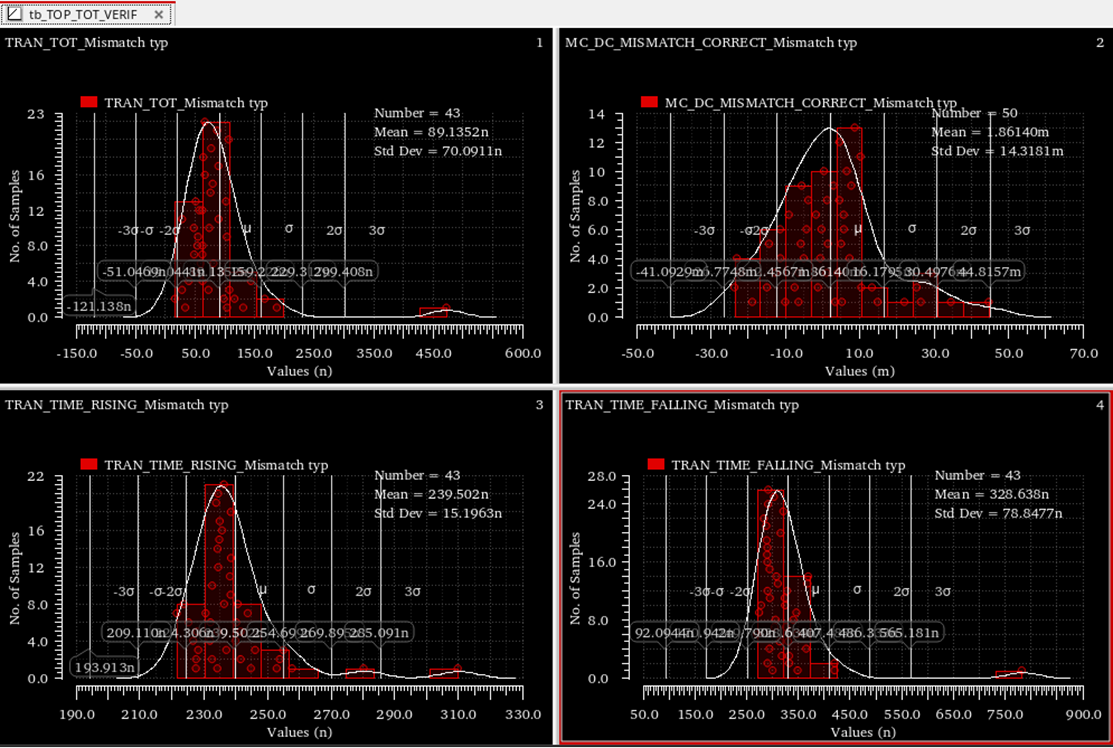

The other simulation I did is finding out the codes that lead to the smallest offset.

But I found out that this scheme produces worse results, i.e., it catches only like 20 out of 50 samples.

If you could inform me any reference regarding this design, I would also like to know.

Design #2 result. two pole system.

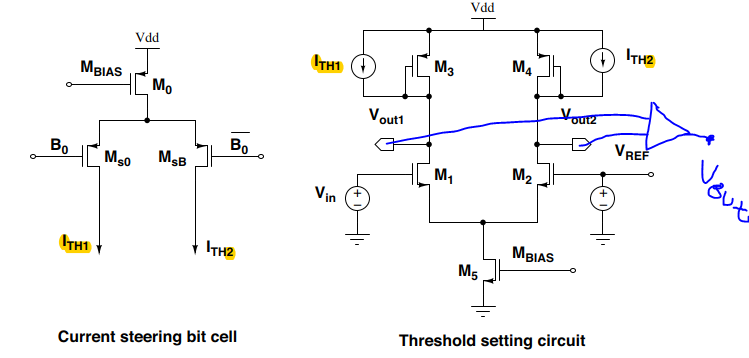

This is the topology. The blue amp is 5-transistor OTA. The inverter follows this OTA (not drawn).

Design #1 result. One pole system, i.e., the output node.

It catches 44 out of 50 samples, but I keep getting very high standard deviation even though I have already made my circuit larger.

How to simulate it correctly?

The other simulation I did is finding out the codes that lead to the smallest offset.

But I found out that this scheme produces worse results, i.e., it catches only like 20 out of 50 samples.

If you could inform me any reference regarding this design, I would also like to know.

Design #2 result. two pole system.

This is the topology. The blue amp is 5-transistor OTA. The inverter follows this OTA (not drawn).

Design #1 result. One pole system, i.e., the output node.