melkord

Full Member level 3

Hi,

I need to simulate and show that the trimming circuit, i.e., 5bit current-output current-steering DAC, reduces the offset of a comparator.

But still confuse with the simulation setup.

I know how to simulate the input offset, but do not know how to simulate the comparator with the trimming circuit.

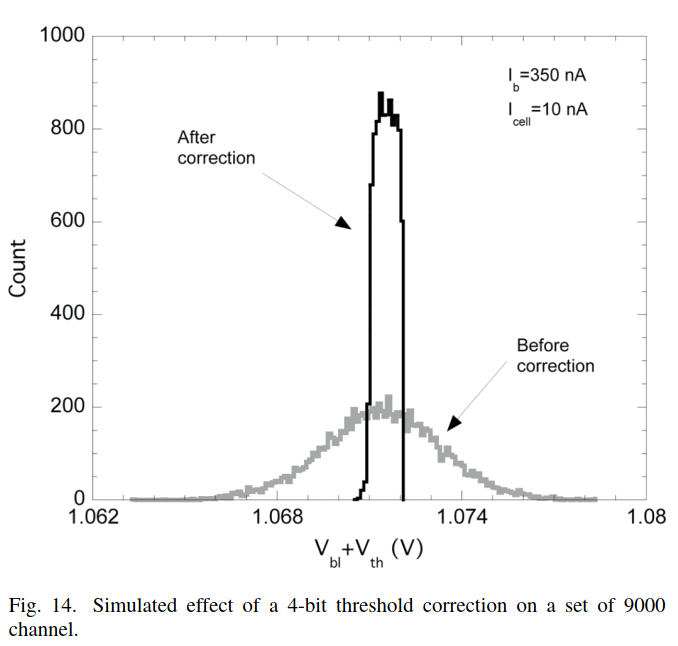

I am expecting something like this in the end:

I need to simulate and show that the trimming circuit, i.e., 5bit current-output current-steering DAC, reduces the offset of a comparator.

But still confuse with the simulation setup.

I know how to simulate the input offset, but do not know how to simulate the comparator with the trimming circuit.

I am expecting something like this in the end: