rmanalo

Advanced Member level 4

- Joined

- Feb 8, 2017

- Messages

- 107

- Helped

- 16

- Reputation

- 32

- Reaction score

- 16

- Trophy points

- 18

- Location

- Philippines

- Activity points

- 979

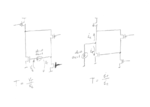

Hello everyone, there's a circuit that is in feedback that I believe is not one of the 4 feedback topologies. I'd like to simulate the feedback loop by putting a break point and inserting a test voltage, Vt, and get the output voltage Vo and measure the feedback loop, Vo/Vt. as seen in the attached figure as an example.

However, if put a break point, would that mean that I need an appropriate value for Vt for the the circuit to function properly (as if the break point didn't exist in the first place)? What are your comments in this method?

However, if put a break point, would that mean that I need an appropriate value for Vt for the the circuit to function properly (as if the break point didn't exist in the first place)? What are your comments in this method?