melkord

Full Member level 3

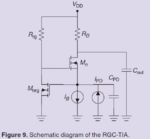

Hi, I think it is time to ask for some help regarding this circuit.

I have this circuit and would like to hear some suggestions on things I can do to reduce the input-referred noise current.

Right now, I can get it around 5-6 pA/sqrt(Hz) with ~400uA,1.8V. I would love to have it below 3, if possible.

Changing gm seems does not work.

So, the suggestion could be any modification of that circuit, while keeping it as common gate.

Other relatively simple topologies with power consumption <~2.0mW(1.8V, ~1200uA, 0.18um) would be as well appreciated.

I have this circuit and would like to hear some suggestions on things I can do to reduce the input-referred noise current.

Right now, I can get it around 5-6 pA/sqrt(Hz) with ~400uA,1.8V. I would love to have it below 3, if possible.

Changing gm seems does not work.

So, the suggestion could be any modification of that circuit, while keeping it as common gate.

Other relatively simple topologies with power consumption <~2.0mW(1.8V, ~1200uA, 0.18um) would be as well appreciated.