fencl

Member level 1

how to realize 3.3v to 1.2v(only can use DC-DC without inductor)

hi,all

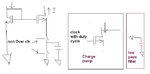

now i need convert 3.3v or 2.5v to 1.2v~1v in cmos0.13um process. if i can't use LDO, only use DC-DC(but without inductor!).how can i do? the ripple need to keep below 50mv.loding up to 30mA .and efficiency > 60~70% is accepted.

Does anyone has relate experience,or some proble way? i need you help, idea, reference papers,or any relate note.

Thanks!

hi,all

now i need convert 3.3v or 2.5v to 1.2v~1v in cmos0.13um process. if i can't use LDO, only use DC-DC(but without inductor!).how can i do? the ripple need to keep below 50mv.loding up to 30mA .and efficiency > 60~70% is accepted.

Does anyone has relate experience,or some proble way? i need you help, idea, reference papers,or any relate note.

Thanks!

Last edited: