henry kissinger

Member level 2

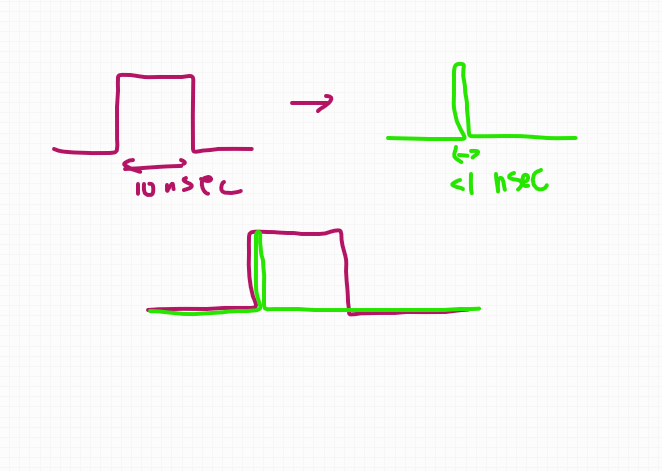

I have a pulse of 10 nesc wide. (low 0V, high 1V)

How do I build a circuit that take this 10 nsec pulse and output a pulse much smaller (<1 nsec)?

The rise point of the 10 nsec pulse and the <1 nsec pulse should be almost the same (<1 nsec difference)

any ideas?

How do I build a circuit that take this 10 nsec pulse and output a pulse much smaller (<1 nsec)?

The rise point of the 10 nsec pulse and the <1 nsec pulse should be almost the same (<1 nsec difference)

any ideas?