gatedriver

Junior Member level 1

Dear all,

How can I extend simulation time in Pspice?

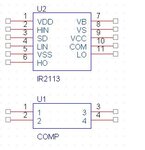

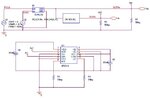

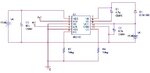

I am doing DC/AC converter with real gate driver.

I also read many convergence problem but I can not solve.

my system has RC circuit time constant: Tau=0.235us

switching frequency: f=5kHz ==> T =0.2ms

output frequency f=60Hz

When I choosed TSTOP = 0.7ms --> It's okie

But I need see the output voltage f=60Hz (T=16.67ms), so when I choose TSTOP =16.67ms --> the convergence problem appear at about 0.42ms, when the swiching device transfer.

I already choose RELTOL = 0.01; VNTOL = 0.01; ABSTOL 0.01u ; CHGTOL = 0.01u; ITL4=40;

Please give me some helps.

Thanks you very much

How can I extend simulation time in Pspice?

I am doing DC/AC converter with real gate driver.

I also read many convergence problem but I can not solve.

my system has RC circuit time constant: Tau=0.235us

switching frequency: f=5kHz ==> T =0.2ms

output frequency f=60Hz

When I choosed TSTOP = 0.7ms --> It's okie

But I need see the output voltage f=60Hz (T=16.67ms), so when I choose TSTOP =16.67ms --> the convergence problem appear at about 0.42ms, when the swiching device transfer.

I already choose RELTOL = 0.01; VNTOL = 0.01; ABSTOL 0.01u ; CHGTOL = 0.01u; ITL4=40;

Please give me some helps.

Thanks you very much