tommydidi

Member level 1

Hi there,

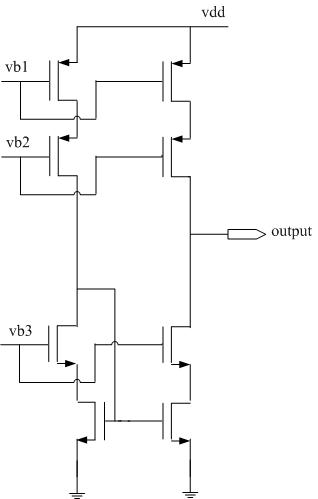

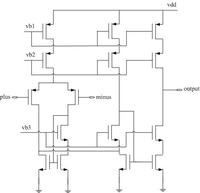

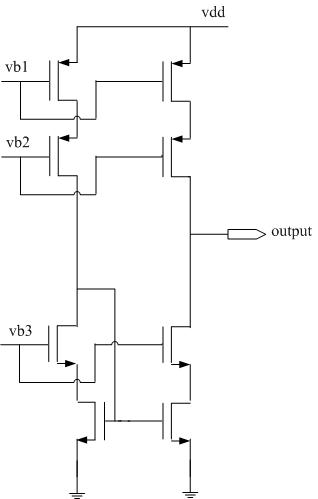

I am designing a two stage opamp (drives a capacitive load) and looking for a way to compensate it. The first stage is a typical pmos input and the second is a cascode one, please see the picture below (only shows the second stage). The "vb1, vb2 and vb3" are bias voltages generated somewhere else in the circuit. I am using the low headroom design for the bottom nmos. I know the cascode opamp is generally self-compensated. After I run the sim, I found the PM is only around 20 degree for some cases. I have played with the cascode pmos and nmos sizes to get the dominant pole moving, it did not help too much though.

I guess I heard a way of compensation by feeding back the output cap, do not know how to do it though. Is it doable? Any other thoughts?

I am designing a two stage opamp (drives a capacitive load) and looking for a way to compensate it. The first stage is a typical pmos input and the second is a cascode one, please see the picture below (only shows the second stage). The "vb1, vb2 and vb3" are bias voltages generated somewhere else in the circuit. I am using the low headroom design for the bottom nmos. I know the cascode opamp is generally self-compensated. After I run the sim, I found the PM is only around 20 degree for some cases. I have played with the cascode pmos and nmos sizes to get the dominant pole moving, it did not help too much though.

I guess I heard a way of compensation by feeding back the output cap, do not know how to do it though. Is it doable? Any other thoughts?