Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

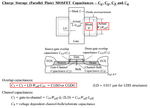

Thanks for your help bro!actually if you wanna find the total CGS thats the gate to source capacitance then first there will be a capacitance from gate to drain(or source) secondly due the the overlap of drain/source just beneath the oxide layer has a certain capacitance thats pretty obviously dependent on the Xd i.e thickness (the overlap) so it would be cgso=Cox*W*Xd now you can get the total source capacitance by adding cgs(i.e capacitance between gate an source other then the overlapping part)+cgso(i.e overlaping one)=CGS

with no channel i meant that its not the one thats dependent on channel its basically the overlap one,when the channel is formed then the current flows and after that the parasitic capacitance (of drain or source could be felt at some conditions).

thirdly,there is a capacitance thats called junction capacitance ,between drain and bulk because the depletion region between drain and bulk serves as a dielectric medium between those two material,but assume that the drain and bulk are at same potential then why would there be any capacitance when theres no opposite polarity of plates?? how could a dipole be formed in a simple capacitor when both plates are at the same charge?? ,so thats what happens when we actually short bulk and source.

bro i cannot find where CGS=CGSO but if its there then it could be because of no potential applied or the potential at drain/source would be so low that its parasitic capacitance might have been neglected for simplicity.

hope it could help