eem2am

Banned

Hi,

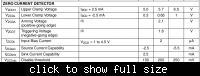

Do you know how long it takes for the L6562 (=transition mode boost PFC IC) to come out of "disable" and start working normally?

i.e. how long after the ZCD pin is pulled above 350mV does it take for the L6562 to resume full functioning?

(that is, supposing that in the first place, the L6562 had been disabled by a switched on NPN on its ZCD pin (pin5) )

L6562 DATASHEET:

https://www.st.com/internet/com/TECHNICAL_RESOURCES/TECHNICAL_LITERATURE/DATASHEET/CD00003316.pdf

Do you know how long it takes for the L6562 (=transition mode boost PFC IC) to come out of "disable" and start working normally?

i.e. how long after the ZCD pin is pulled above 350mV does it take for the L6562 to resume full functioning?

(that is, supposing that in the first place, the L6562 had been disabled by a switched on NPN on its ZCD pin (pin5) )

L6562 DATASHEET:

https://www.st.com/internet/com/TECHNICAL_RESOURCES/TECHNICAL_LITERATURE/DATASHEET/CD00003316.pdf