BackerShu

Member level 3

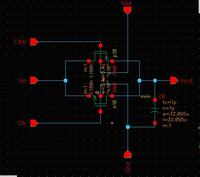

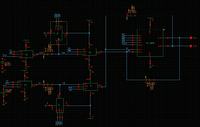

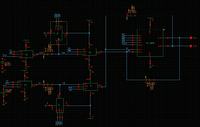

Hello, guys! I have a SC integrator shown as following.

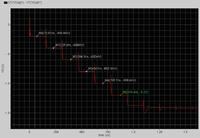

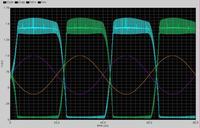

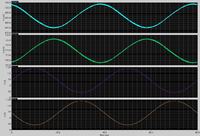

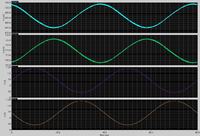

I want to fix the gain at 1/2. So I set C1 and C2 at 2.5pF, C3 and C4 at 5pF, and the gain will be C1/C3=1/2 theoretically. When I give input signal biased at 700mv of which the amplitude 500mV, and the frequency is 25KHz. The simulation result turns out to be like this.

The question is I don't know whether the gain of the integrator is 1/2. And how could I know the exact gain is through the result? Please help me, thanks in advance.

Best wishes!

I want to fix the gain at 1/2. So I set C1 and C2 at 2.5pF, C3 and C4 at 5pF, and the gain will be C1/C3=1/2 theoretically. When I give input signal biased at 700mv of which the amplitude 500mV, and the frequency is 25KHz. The simulation result turns out to be like this.

The question is I don't know whether the gain of the integrator is 1/2. And how could I know the exact gain is through the result? Please help me, thanks in advance.

Best wishes!