gdylp2004

Member level 5

Hi guys,

I'm new in here and hope I could get some advices.

I am designing a 100V-28V DC-DC Buck converter but has encountered a problem when choosing a suitable high-frequency switch. As suggested by many designers online, pMOS is preferred for Buck operation. However one big issue is the limitation of the Vgs (typ: +-20V) which I believe is the reason why I could not utilize this as what other designers usually do.

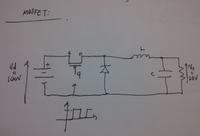

As seen in the attached schematic, in order to turn off the pMOS switch, Vg must not be lower than both Vs and Vd by the threshold voltage indicated by the manufacturer. That is, |Vgs|< |Vth| & |Vgd| < |Vth|. Since Vs is always 100V (because source is tied to +ve terminal of battery) and Vd = 28V (assuming the capacitor is large enough to hold the charge, hence o/p voltage well) and assuming the Vth is -4V, is it correct that to turn switch off, Vg must be > Vs-|Vth| and also Vg > Vd-|Vth| since a pure MOSFET drain and source is interchangeable.

If this is true, a typical pMOS with only Vgs max of 20V could not handle since we must ramp up Vg all the way to 96V and above (for my case) but that also implies the potential difference between Vg and Vd is 68V which is > 20V and thus the FET will breakdown.

Assuming my source (Vs) and drain voltage (Vd) is always held constant at 100V and 28V respectively, and also assume the pMOS has a threshold voltage of a typical value of -4V. In order to cut off the switch totally, we knew Vg (gate voltage) must be at least > 96V since criteria for MOSFET to operate in the cutoff region is |Vgs| < |Vth|.

And in this particular case, assuming I've set Vg = 100V so that Vgs would be 0 and Vg is so much higher than Vd (about 100-28=72V), therefore both side would not be conducting and hence pMOS operate into the cut-off region. Now, this 72V across the gate and drain is my biggest concern because the manufacturer stated max Vgs = 20V, and since a MOSFET drain and source is interchangeable, therefore I should also assume that the max Vgs also implies the max of Vgd? And if true, shouldn't the Zener diode should protect the potential between gate and drain instead of gate and source?

And if everything I've explained is true, is there a way to overcome this? TIA.

I'm new in here and hope I could get some advices.

I am designing a 100V-28V DC-DC Buck converter but has encountered a problem when choosing a suitable high-frequency switch. As suggested by many designers online, pMOS is preferred for Buck operation. However one big issue is the limitation of the Vgs (typ: +-20V) which I believe is the reason why I could not utilize this as what other designers usually do.

As seen in the attached schematic, in order to turn off the pMOS switch, Vg must not be lower than both Vs and Vd by the threshold voltage indicated by the manufacturer. That is, |Vgs|< |Vth| & |Vgd| < |Vth|. Since Vs is always 100V (because source is tied to +ve terminal of battery) and Vd = 28V (assuming the capacitor is large enough to hold the charge, hence o/p voltage well) and assuming the Vth is -4V, is it correct that to turn switch off, Vg must be > Vs-|Vth| and also Vg > Vd-|Vth| since a pure MOSFET drain and source is interchangeable.

If this is true, a typical pMOS with only Vgs max of 20V could not handle since we must ramp up Vg all the way to 96V and above (for my case) but that also implies the potential difference between Vg and Vd is 68V which is > 20V and thus the FET will breakdown.

Assuming my source (Vs) and drain voltage (Vd) is always held constant at 100V and 28V respectively, and also assume the pMOS has a threshold voltage of a typical value of -4V. In order to cut off the switch totally, we knew Vg (gate voltage) must be at least > 96V since criteria for MOSFET to operate in the cutoff region is |Vgs| < |Vth|.

And in this particular case, assuming I've set Vg = 100V so that Vgs would be 0 and Vg is so much higher than Vd (about 100-28=72V), therefore both side would not be conducting and hence pMOS operate into the cut-off region. Now, this 72V across the gate and drain is my biggest concern because the manufacturer stated max Vgs = 20V, and since a MOSFET drain and source is interchangeable, therefore I should also assume that the max Vgs also implies the max of Vgd? And if true, shouldn't the Zener diode should protect the potential between gate and drain instead of gate and source?

And if everything I've explained is true, is there a way to overcome this? TIA.