ngmedaboard

Member level 3

- Joined

- Feb 7, 2010

- Messages

- 60

- Helped

- 7

- Reputation

- 14

- Reaction score

- 4

- Trophy points

- 1,288

- Location

- United States

- Activity points

- 1,831

To the board:

Objetive:

We looking to build an AC power supply with the following characteristics:

Voltage: 500V pk-pk

Waveform: Square

Duty Cycle: 50% for now

Frequency: 30Khz

Load: 0 - 12mA RMS somewhat capacitive

Note: We are currently testing the circuit open circuit so the load is not a factor in the problems currently being encountered. I have merely mentioned it as any design solution should not preclude the ability to supply the above mentioned currents.

Challenge:

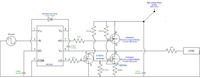

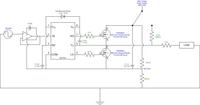

We don't currently have an AC supply or amplifier so are looking to construct a level shifter circuit. We have a high voltage DC supply, function generator and high speed high voltage switching FET **broken link removed** and have come up with the following approach which has not worked as well as we had hoped.

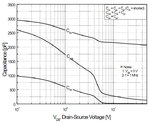

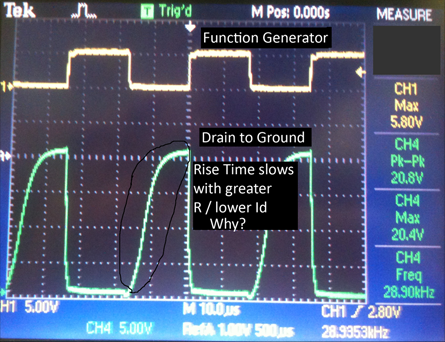

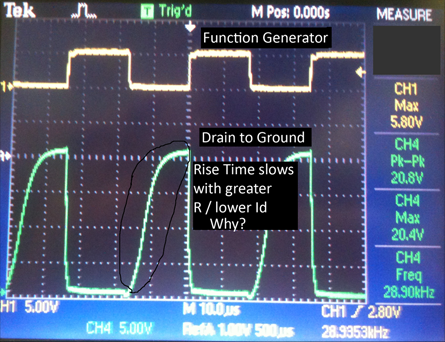

The biggest problem we have noticed is that if the resistance connecting the power supply to the drain is too high or in other works Id is too low, the rise time of the FET begins to suffer dramatically. Of course this only increases as the frequency is pushed beyond 1khz and up towards 30khz.

My prior experience with FETs has never led me to believe there is any benefit to their switching characteristics from increasing Id and thus I'd like to ask what might be happening hear that I am not considering?

I had anticipated my resistor selection here to be merely a factor of the DC supply voltage and my desired load current.

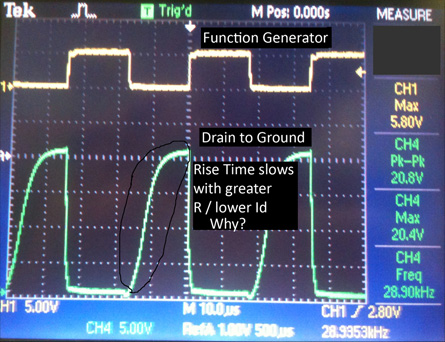

The following is a graph of what we're seeing with only a 20Vdc supply, a 5k resistor open circuit (no load). It's not terrible but you can already see a slow rise time.

Any additional thoughts or recommendations are greatly appreciated.

---------- Post added at 21:24 ---------- Previous post was at 20:33 ----------

I'll note that we also poked around quite a bit looking for any stray capacitance that could have been in the circuit and couldn't find anything.

---------- Post added at 21:36 ---------- Previous post was at 21:24 ----------

Also thought about using a push pull arrangement but don't believe we had much luck finding a complimentary pair of FETs rated for the voltages in play here at least not for a high speed application. I suppose it could be done using a push pull pair with a step-up transformer on the output, but we'd like to avoid the need for a transformer if the more basic level shifter is possible.

Objetive:

We looking to build an AC power supply with the following characteristics:

Voltage: 500V pk-pk

Waveform: Square

Duty Cycle: 50% for now

Frequency: 30Khz

Load: 0 - 12mA RMS somewhat capacitive

Note: We are currently testing the circuit open circuit so the load is not a factor in the problems currently being encountered. I have merely mentioned it as any design solution should not preclude the ability to supply the above mentioned currents.

Challenge:

We don't currently have an AC supply or amplifier so are looking to construct a level shifter circuit. We have a high voltage DC supply, function generator and high speed high voltage switching FET **broken link removed** and have come up with the following approach which has not worked as well as we had hoped.

The biggest problem we have noticed is that if the resistance connecting the power supply to the drain is too high or in other works Id is too low, the rise time of the FET begins to suffer dramatically. Of course this only increases as the frequency is pushed beyond 1khz and up towards 30khz.

My prior experience with FETs has never led me to believe there is any benefit to their switching characteristics from increasing Id and thus I'd like to ask what might be happening hear that I am not considering?

I had anticipated my resistor selection here to be merely a factor of the DC supply voltage and my desired load current.

The following is a graph of what we're seeing with only a 20Vdc supply, a 5k resistor open circuit (no load). It's not terrible but you can already see a slow rise time.

Any additional thoughts or recommendations are greatly appreciated.

---------- Post added at 21:24 ---------- Previous post was at 20:33 ----------

I'll note that we also poked around quite a bit looking for any stray capacitance that could have been in the circuit and couldn't find anything.

---------- Post added at 21:36 ---------- Previous post was at 21:24 ----------

Also thought about using a push pull arrangement but don't believe we had much luck finding a complimentary pair of FETs rated for the voltages in play here at least not for a high speed application. I suppose it could be done using a push pull pair with a step-up transformer on the output, but we'd like to avoid the need for a transformer if the more basic level shifter is possible.

Last edited: