esoteric1

Newbie level 4

Hi

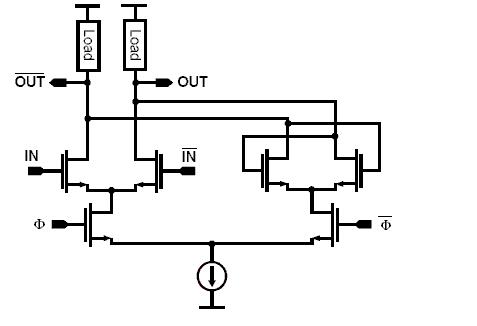

I am trying to design a CML/SCL latch. If I want a 700mv output swing, I assumed that the common mode input range of the latch for "IN" is atleast from VDD to 'VDD-0.7V'. The reasoning behind my assumption is that I will use the latch to form a Flip-Flop and a divider which requires the out_bar to connect to DIN. What should the common mode range of the CLK be? I am using biased current sources(pmos devices) as load devices.

How do I simulate the differential gain of this circuit in hspice? and how do I go about calculating the device sizes for this circuit?

Your comments are much appreciated!

I am trying to design a CML/SCL latch. If I want a 700mv output swing, I assumed that the common mode input range of the latch for "IN" is atleast from VDD to 'VDD-0.7V'. The reasoning behind my assumption is that I will use the latch to form a Flip-Flop and a divider which requires the out_bar to connect to DIN. What should the common mode range of the CLK be? I am using biased current sources(pmos devices) as load devices.

How do I simulate the differential gain of this circuit in hspice? and how do I go about calculating the device sizes for this circuit?

Your comments are much appreciated!