ljp2706

Full Member level 2

Is it possible to make a digital ripple counter out of 6T SRAM cells? I’m trying to make the most area compact architecture I can find. I need to have asynchronous reset capabilities and the ability to latch each output value without interfering with counting. Right now the best I can do is a transmission gate DFF architecture. Two D latches with reset for the DFF and one D latch for the output latching to store the value. Total of 30 transistors per bit. I cannot use dynamic architectures because the counter needs to go for several milliseconds. To get this to fit in my application I really need to drive this number down to 15-20 transistors.

I’m starting to think this isn’t possible to implement with so few devices and I may have to revisit the overall architecture of the system to accommodate using less bits.

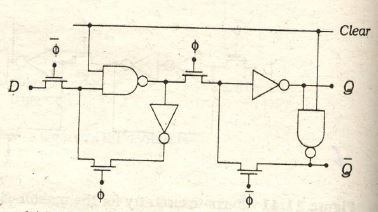

This snippet from online is essentially what I have for the DFF but I implement t-gates instead of pass gates.

I’m starting to think this isn’t possible to implement with so few devices and I may have to revisit the overall architecture of the system to accommodate using less bits.

This snippet from online is essentially what I have for the DFF but I implement t-gates instead of pass gates.