PEEMONGER

Newbie

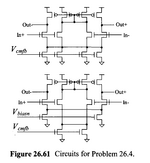

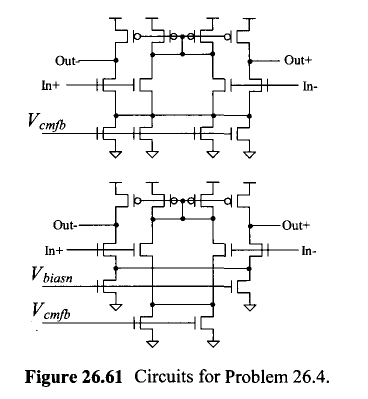

I am trying to figure out problem 26.4 from Baker's book, CMOS: Circuit Design, Layout, and Simulation. I am taking an introductory CMOS design course and I could use some help with this question. I am trying to compare these two circuits:

My initial guesses had to do with the difference in influence of CMFB between the two circuits and how that impacts stability. That or the difference in the relationship between Vcmfb and the commond-mode output voltage.

In transient simulation, both circuits function similarly and when I put in a very small step response, they both seem to stop functioning in the same way (the output common mode voltage increases drastically). The only confident distinction I can make is that increasing Vcmfb causes output common-mode to decrease in top circuit and increase in bottom circuit.

Link to chapter:

If you have any insight into what I should expect, I would appreciate it. I do not know if my designs are at fault or if the topologies are flawed, or both. Thank you!

My initial guesses had to do with the difference in influence of CMFB between the two circuits and how that impacts stability. That or the difference in the relationship between Vcmfb and the commond-mode output voltage.

In transient simulation, both circuits function similarly and when I put in a very small step response, they both seem to stop functioning in the same way (the output common mode voltage increases drastically). The only confident distinction I can make is that increasing Vcmfb causes output common-mode to decrease in top circuit and increase in bottom circuit.

Link to chapter:

If you have any insight into what I should expect, I would appreciate it. I do not know if my designs are at fault or if the topologies are flawed, or both. Thank you!