Coper

Member level 4

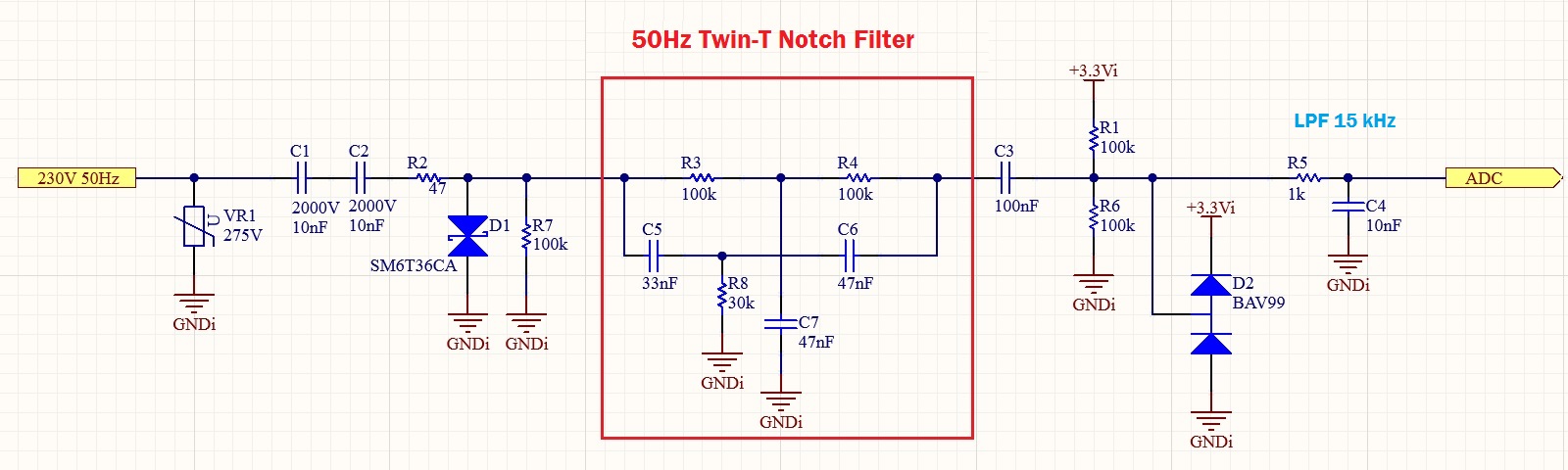

For remote control of electrical equipment, we use a signal with a frequency of 250 - 1000 Hz, which is mixed with the mains voltage 230V 50Hz. I connected via a 230 / 6.5V transformer, MCU with ADC and with the help of tone analysis I can detect and decode control signals.However, the transformer is relatively large and has a relatively large consumption. I want to try another solution.

My solution

VR1 Safty

C1 C2 They reduce the voltage, with 50Hz reducing more and higher frequencies and providing a voltage resistance of 4000V

R2 small size resistance as safety fuse

D1 Safety

R7 ensures minimum current through C1, C2

50Hz Twin-T Norch filter suppressing 50Hz and thus increasing the weight of the higher frequency signal

C3 ,R1/R6 DC isolation and signal shift 0-3.3V

D2 Safety

R5 C4 LPF cutting frequency over 15kHz

According to the simulations, it works as I assume, but I wonder if I'm not exaggerating and it's not possible to throw something out of it?

In short, I am interested in your opinion and suggestions on what to do differently?

Thank you in advance

My solution

VR1 Safty

C1 C2 They reduce the voltage, with 50Hz reducing more and higher frequencies and providing a voltage resistance of 4000V

R2 small size resistance as safety fuse

D1 Safety

R7 ensures minimum current through C1, C2

50Hz Twin-T Norch filter suppressing 50Hz and thus increasing the weight of the higher frequency signal

C3 ,R1/R6 DC isolation and signal shift 0-3.3V

D2 Safety

R5 C4 LPF cutting frequency over 15kHz

According to the simulations, it works as I assume, but I wonder if I'm not exaggerating and it's not possible to throw something out of it?

In short, I am interested in your opinion and suggestions on what to do differently?

Thank you in advance