abuzaid10

Junior Member level 1

Hello,

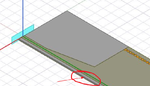

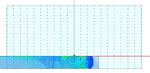

I am having a problem on simulating a half-mode SIW in HFSS.

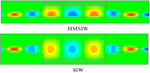

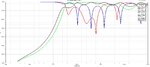

Since we cut the width by half, the resulting structure has cut-off frequency double the original one.

But all papers said they have very close responses.

Any idea how should I simulate the half-mode structure?

Thank you for your help!

I am having a problem on simulating a half-mode SIW in HFSS.

Since we cut the width by half, the resulting structure has cut-off frequency double the original one.

But all papers said they have very close responses.

Any idea how should I simulate the half-mode structure?

Thank you for your help!