yefj

Advanced Member level 5

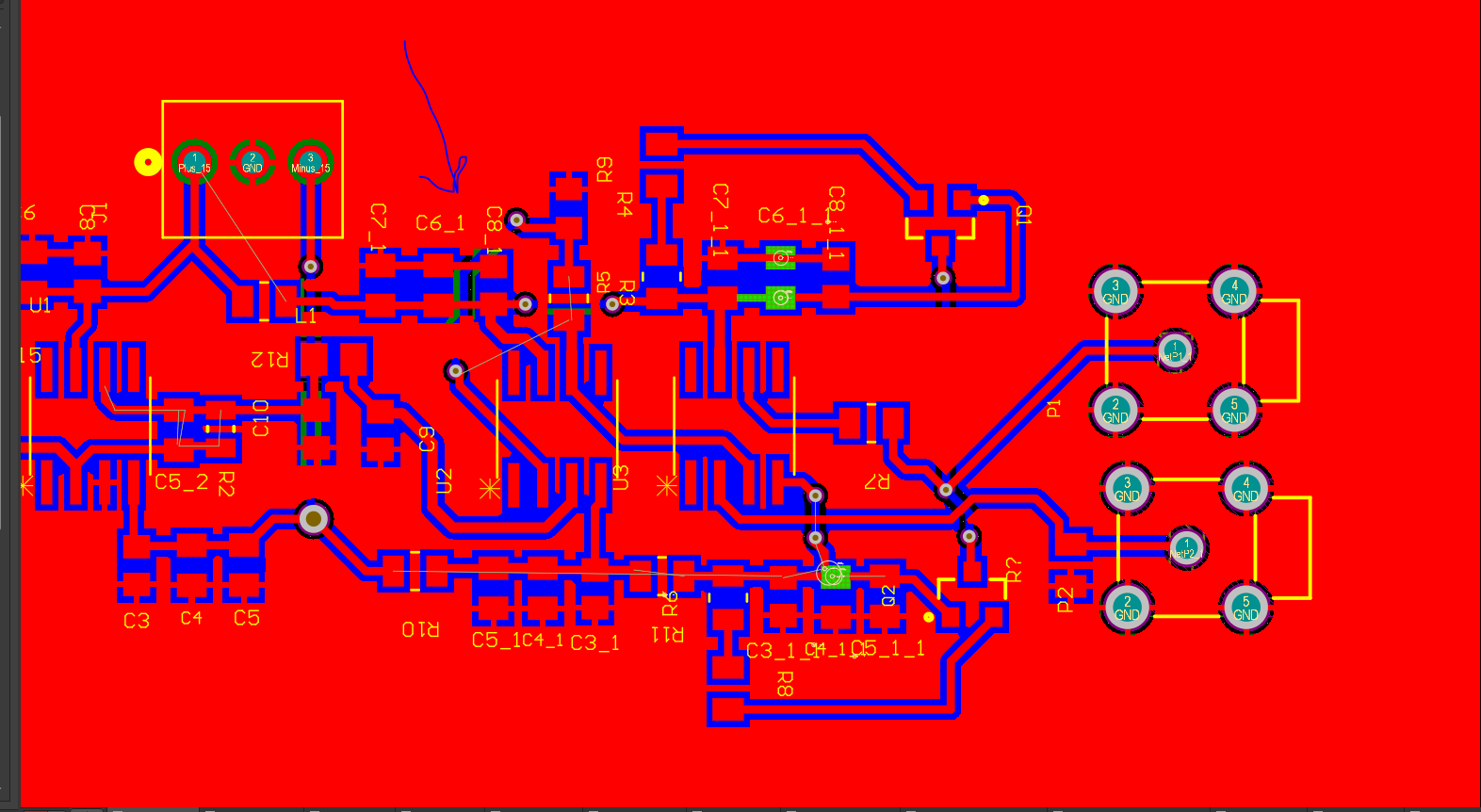

Hello,As you can see i have section of a circuit in which the traces of DC and traces of a signal pass threw bottom layer.

te problem is that is it passes threw buttom layer it needs a solid GND layer on the top layer and in the section shown i the blue arrow i dont have much GND for the little section of trace shown below in the arrow.

How do i know if it will cause problems?

what are the alternatives?

Thanks.

Top layer:

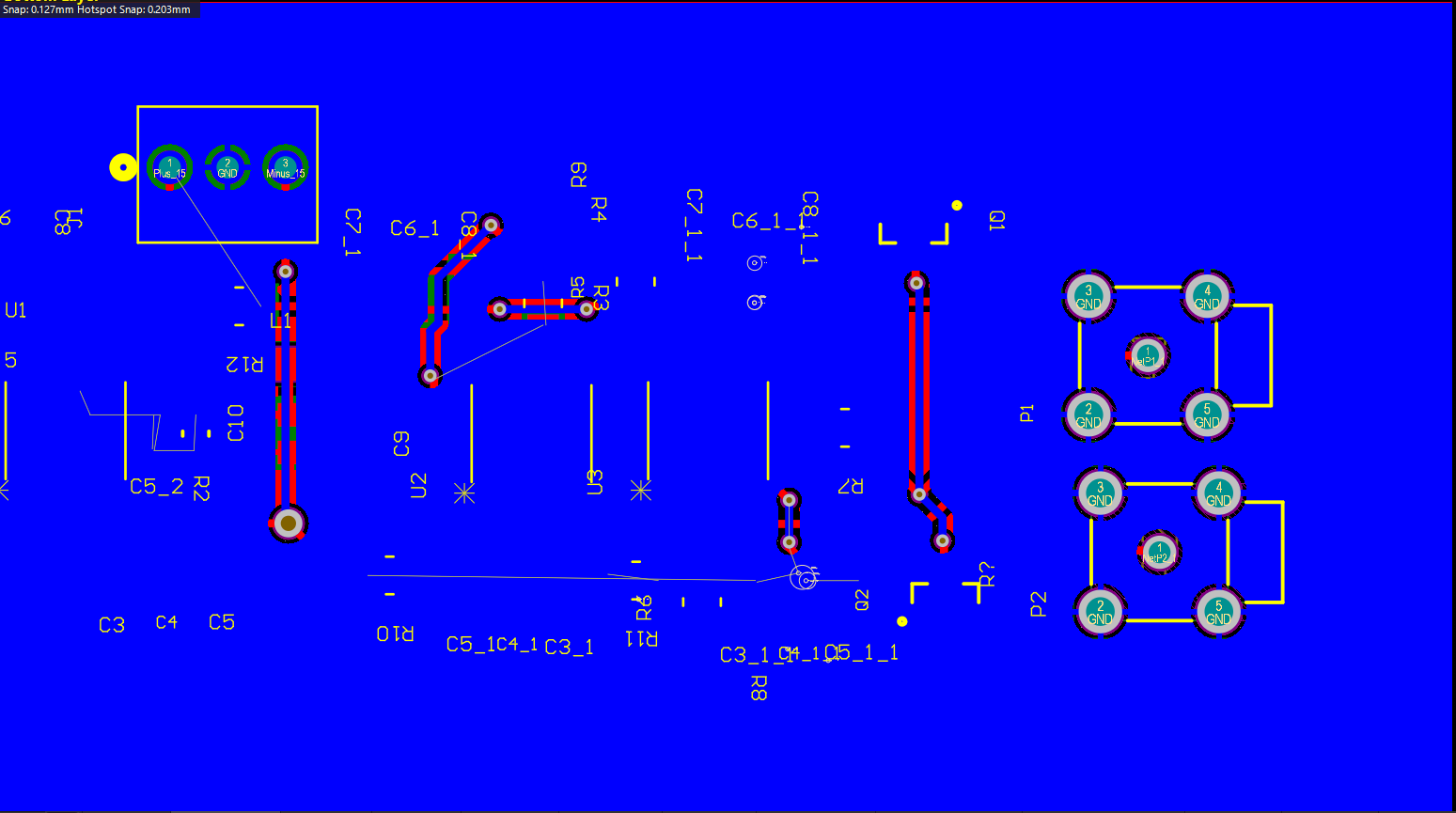

Buttom layer:

te problem is that is it passes threw buttom layer it needs a solid GND layer on the top layer and in the section shown i the blue arrow i dont have much GND for the little section of trace shown below in the arrow.

How do i know if it will cause problems?

what are the alternatives?

Thanks.

Top layer:

Buttom layer: