narayani

Full Member level 2

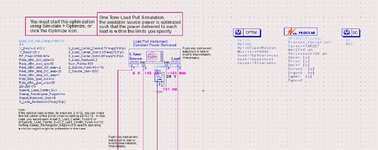

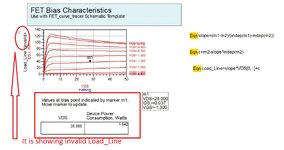

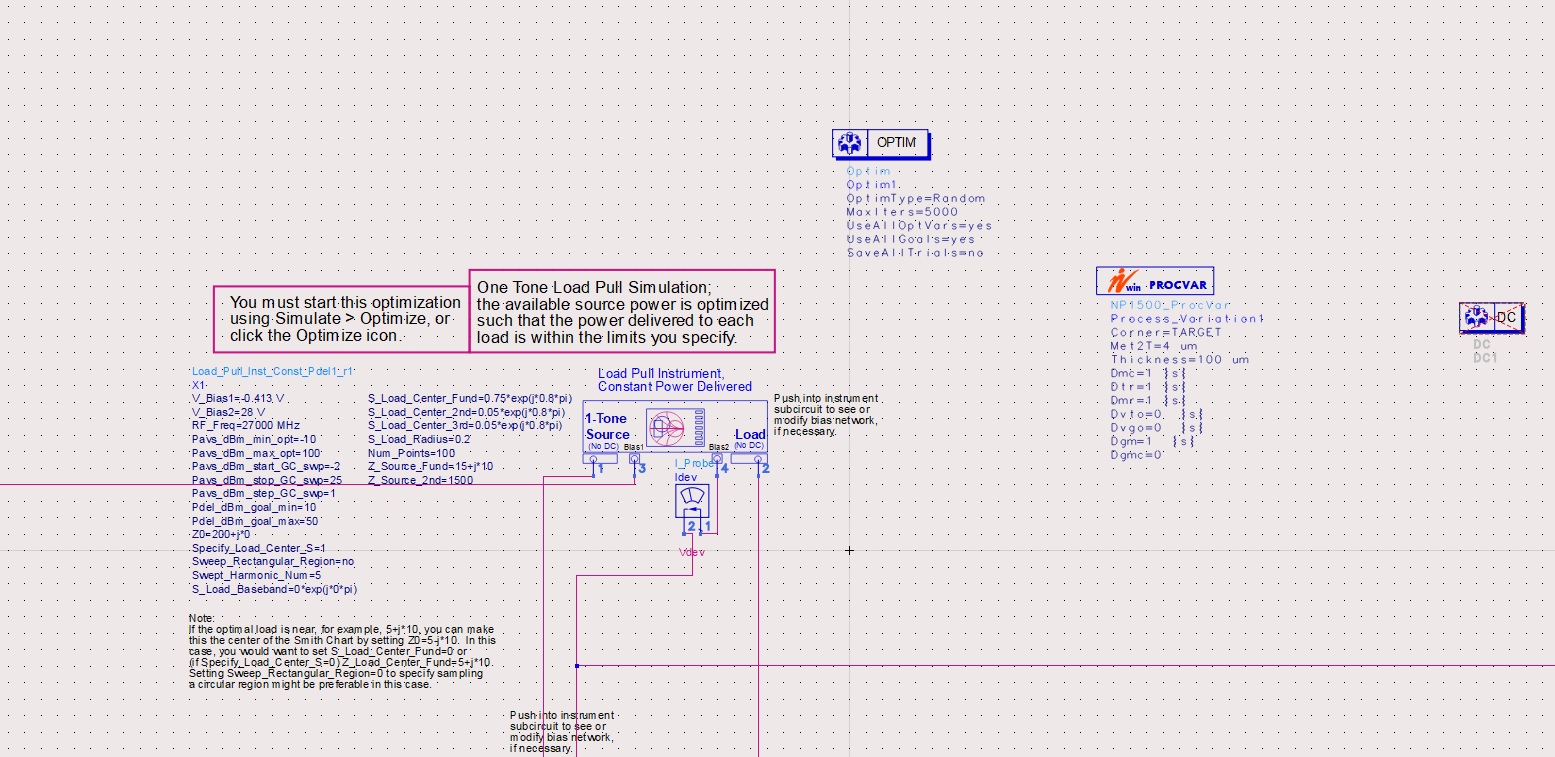

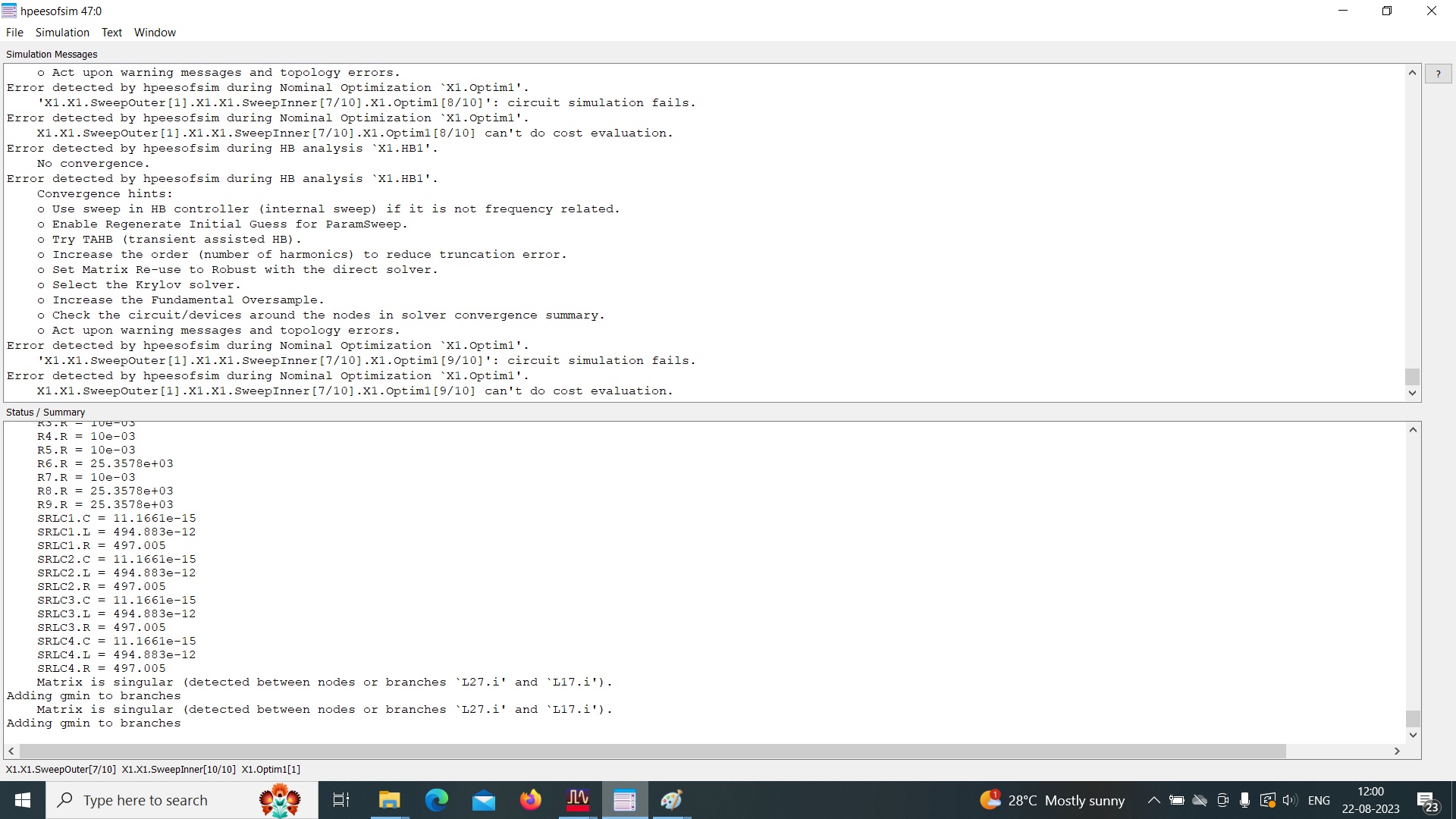

I am designing Power Amplifier at 27GHz. When I used template of one tone, constant power Delivered Load Pull and started executing, I am getting many errors. How to get out of this error? Error related screen shots are attached.

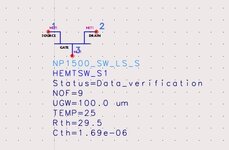

But when I connected template to only transistor. I didn't get any error at all. When I connected template to Power Amplifier Circuit. I am getting error.

But when I connected template to only transistor. I didn't get any error at all. When I connected template to Power Amplifier Circuit. I am getting error.