narayani

Full Member level 2

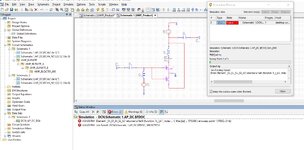

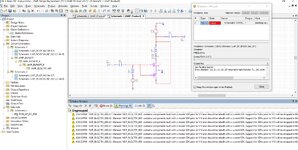

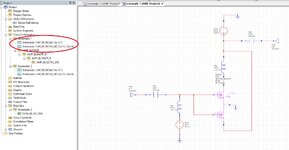

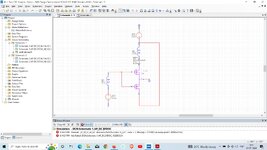

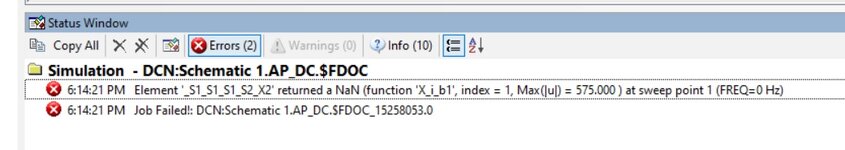

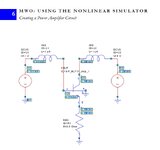

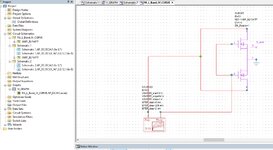

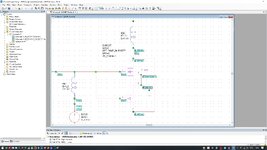

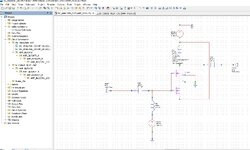

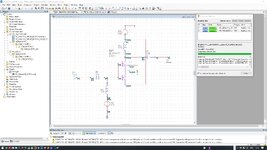

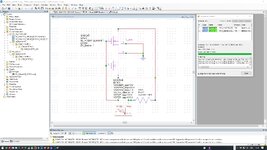

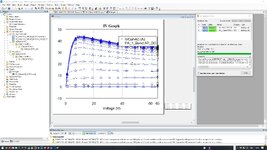

I am getting error during annotation of DC Voltage and current using AWR MWO. I am not able to find out how to get rid of this error. Actually I wanted to check biasing condition for Power Amplifier.