Akshe

Junior Member level 2

Hi,

I have a few doubts about the MOSFETs in general-

1. What is the drain voltage when the MOS is in different modes of operation (saturation,linear and subthreshold). There is a finite current being sourced or sunk by the device and 1 terminal of the device is at Vdd or gnd.

2. In the case of NMOS where we have Vdd at one terminal and Vgate is Vdd too, the voltage at the other terminal can be max Vdd-Vthn. Is this valid only for saturation region operation?

Similarly for the PMOS when there is 0 at Vgate and one of the terminal , the other terminal can have Vthp as the minimum voltage. Is this also valid only for the saturation region?

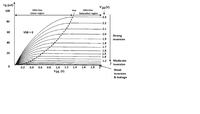

3. Is this correct-

weak inversion = Subthreshold mode (Vgs<Vth)

Onset of strong inversion = Vgs = Vth

Strong inversion = Linear and Saturation mode

Any good references to help get these answers will also be helpful.:roll:

I have a few doubts about the MOSFETs in general-

1. What is the drain voltage when the MOS is in different modes of operation (saturation,linear and subthreshold). There is a finite current being sourced or sunk by the device and 1 terminal of the device is at Vdd or gnd.

2. In the case of NMOS where we have Vdd at one terminal and Vgate is Vdd too, the voltage at the other terminal can be max Vdd-Vthn. Is this valid only for saturation region operation?

Similarly for the PMOS when there is 0 at Vgate and one of the terminal , the other terminal can have Vthp as the minimum voltage. Is this also valid only for the saturation region?

3. Is this correct-

weak inversion = Subthreshold mode (Vgs<Vth)

Onset of strong inversion = Vgs = Vth

Strong inversion = Linear and Saturation mode

Any good references to help get these answers will also be helpful.:roll: