Centmo

Member level 3

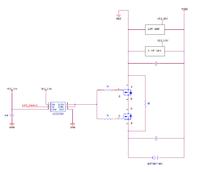

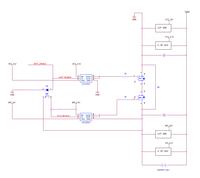

Hi, looking for some advice here. My system has two independent batteries connected, each with their own power-disconnect switch. Since current cannot be allowed to flow either way through the switch when off, two MOSFETs are used in a source-to-source configuration to create a bi-directional switch. My question is, how to achieve the gate drive of these FETs. They need to be able to be fully on (100% duty cycle) or off for extended periods of time. I don't expect that the attached schematic will work because the FET sources are floating when off. Note the 80ohm bypass which keeps the board MCU and voltage regulators powered even when the switches are off. Any suggestions?

Thanks.

Thanks.