daintyvlsi

Newbie level 2

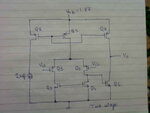

We are trying to simulate a two stage op-amp of Sedra Smith. But we get gain of around 12 dB. Can anyone please tell the ideal region of operation of different MOS alongwith diagram so as to get maximum gain, as soon as possible?