chikaofili

Junior Member level 3

Hello,

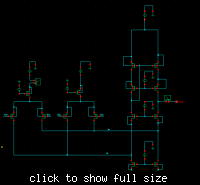

I have an assignment for a DDA (Differential Difference Ampplifer) where

Vo= A( (Vpp-Vpn) -( Vnp - Vnn))

Hence Vo= A[(Vpp+Vnn) - (Vpn+Vnp)]

Then I have two input different stage that then add before it gets into the folded cascode stage (Hope I am making sense)

But I have the following specs

Vdd= 1.8v

Total current=150uA

Vpn:Vnn= 0- 0.9V

Phase Margin: >45deg

Gain: >60dB

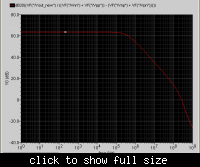

At this point, my design is embarrassing. I can only get the voltage up to 50dB.

And the phase margin is worse -39deg

I know that the A= Gm Rout

and to improve Gm: I have to increase the W/L or/and I of the input stage

and the Rout of the differential stage.

But with the restriction of the power consumption, I am kinda at a dead end. <~ Maybe I should crank up the current and disregard the restriction?

I used the parameter sweep to get the Widths of the various pmos and nmos of the cascode stage.

How can I improve the phase margin?

Any help/suggestion will be appreciated.

Thanks

* I attached pictures

I have an assignment for a DDA (Differential Difference Ampplifer) where

Vo= A( (Vpp-Vpn) -( Vnp - Vnn))

Hence Vo= A[(Vpp+Vnn) - (Vpn+Vnp)]

Then I have two input different stage that then add before it gets into the folded cascode stage (Hope I am making sense)

But I have the following specs

Vdd= 1.8v

Total current=150uA

Vpn:Vnn= 0- 0.9V

Phase Margin: >45deg

Gain: >60dB

At this point, my design is embarrassing. I can only get the voltage up to 50dB.

And the phase margin is worse -39deg

I know that the A= Gm Rout

and to improve Gm: I have to increase the W/L or/and I of the input stage

and the Rout of the differential stage.

But with the restriction of the power consumption, I am kinda at a dead end. <~ Maybe I should crank up the current and disregard the restriction?

I used the parameter sweep to get the Widths of the various pmos and nmos of the cascode stage.

How can I improve the phase margin?

Any help/suggestion will be appreciated.

Thanks

* I attached pictures