viperpaki007

Full Member level 5

Hi,

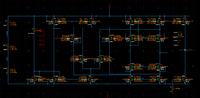

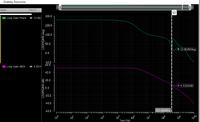

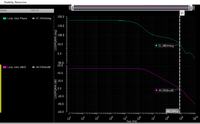

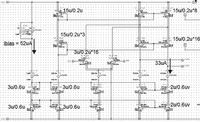

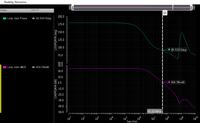

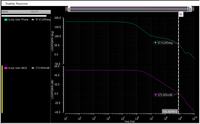

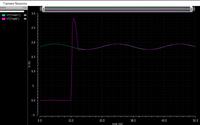

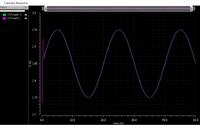

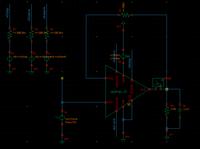

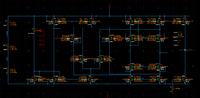

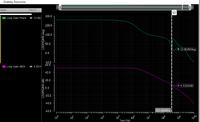

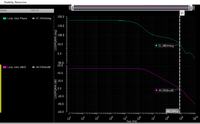

I have designed a folded cascode two stage opamp on 130nm process. The opamp works fine. Figure below shows the gain and phase response of opamp. It has 45 degree phase margin. Now the next step is to design circuit which generated the bias voltages for opamp. For initial case i used a resistive voltage divider to generate bias voltages (as shown in figure below). However, as soon as i generate bias voltages using a resistive voltage divider, my stabilty response becomes really poor. See figure below. I have no clue why that happens. Can somebody explain the degradation of stability response by adding resistive divider for biasing. What should be the right way to bias the opamp.

regards

I have designed a folded cascode two stage opamp on 130nm process. The opamp works fine. Figure below shows the gain and phase response of opamp. It has 45 degree phase margin. Now the next step is to design circuit which generated the bias voltages for opamp. For initial case i used a resistive voltage divider to generate bias voltages (as shown in figure below). However, as soon as i generate bias voltages using a resistive voltage divider, my stabilty response becomes really poor. See figure below. I have no clue why that happens. Can somebody explain the degradation of stability response by adding resistive divider for biasing. What should be the right way to bias the opamp.

regards